用CPLD支持多個SD器件

在一個系統中添加多個安全數字 (SD) 器件的需求日益增長。然而,大多數主機器件(如 Intel PXA270、TI OMAP和Qualcomm MSM處理器)都只提供一個SD接口。幸運的是,使用復雜可編程邏輯器件(CPLD)即可使主機器件支持任意數量的SD器件。本文詳細講述一種基于可縮放自動偵測雙向多路復用器的設計。

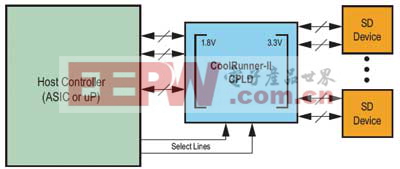

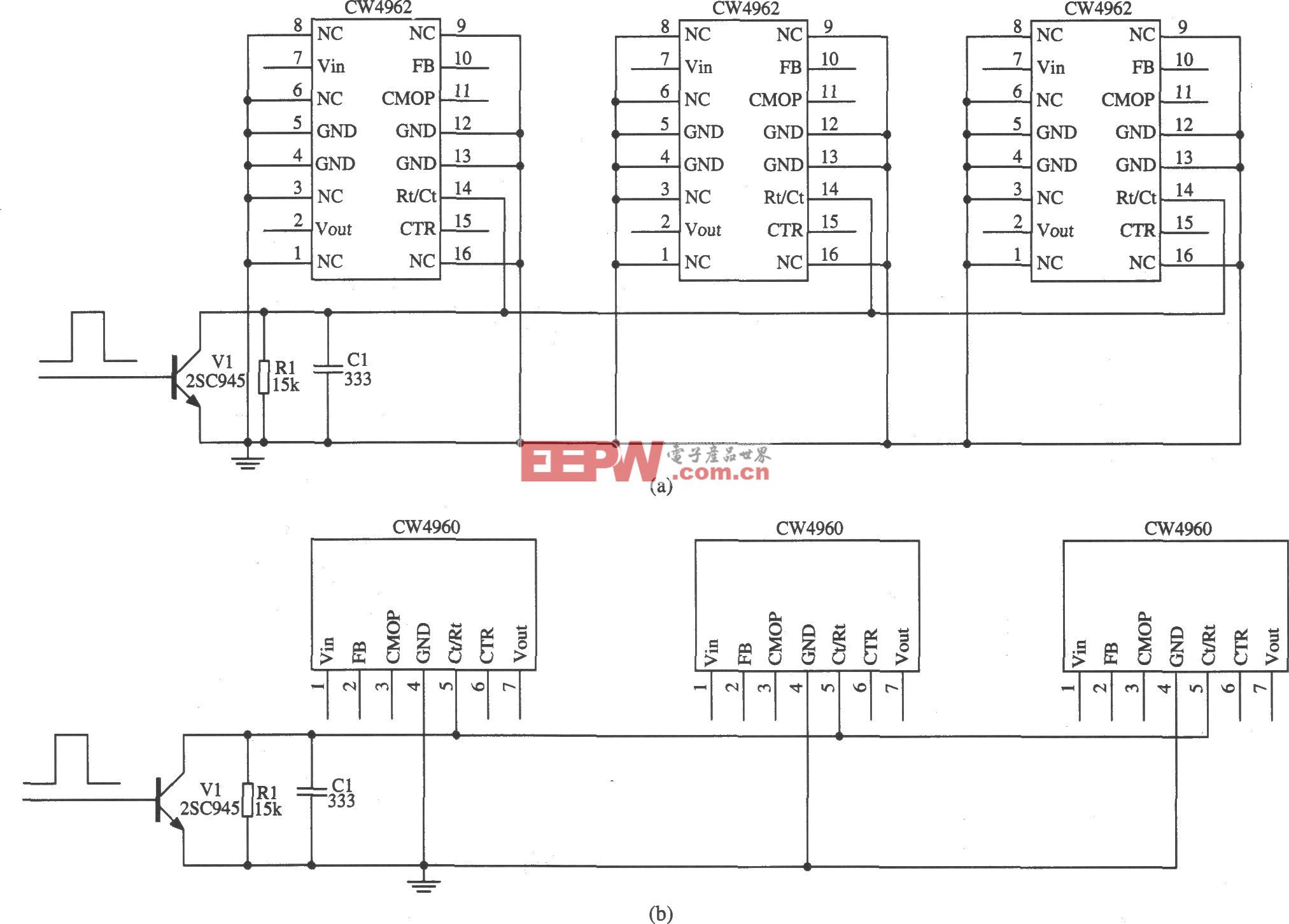

本文引用地址:http://www.104case.com/article/152101.htm圖1所示為通用的CPLD使用模型,可以為僅自帶一個SD接口的給定主機器件集成任意數量的SD端口。CPLD處于主機控制器和SD器件之間。這樣,CPLD便起到雙向多路復用器的作用,使主機器件能夠與選定的任意SD器件通信。更重要的是,這種設計沒有方向控制引腳,也就是說CPLD自動檢測數據流方向。

圖1 用CPLD增加SD端口

圖1 用CPLD增加SD端口

這種實現方法極其靈活且可縮放,允許隨意增減SD端口數量,還支持SPI模式、1位數據模式和 4 位數據模式中任一種定義的SD卡模式。

在此類應用中使用CPLD器件,主要目的是為主機控制器提供更多的SD端口,同時在主機器件與SD卡之間實現電平轉換和邏輯隔離。圖1所示為主機器件是1.8V而 SD器件是3.3V的情形。業界最新CPLD的待機電流微不足道,而動態功耗極低。因此,在系統中集成一個復雜可編程邏輯器件不會顯著影響功率預算。

符合SDA規范

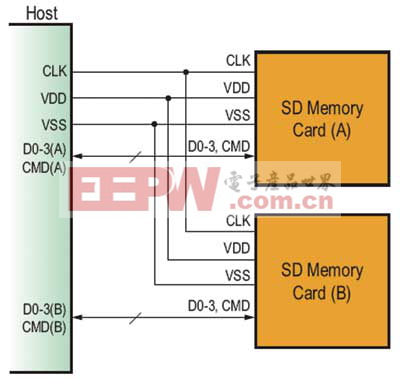

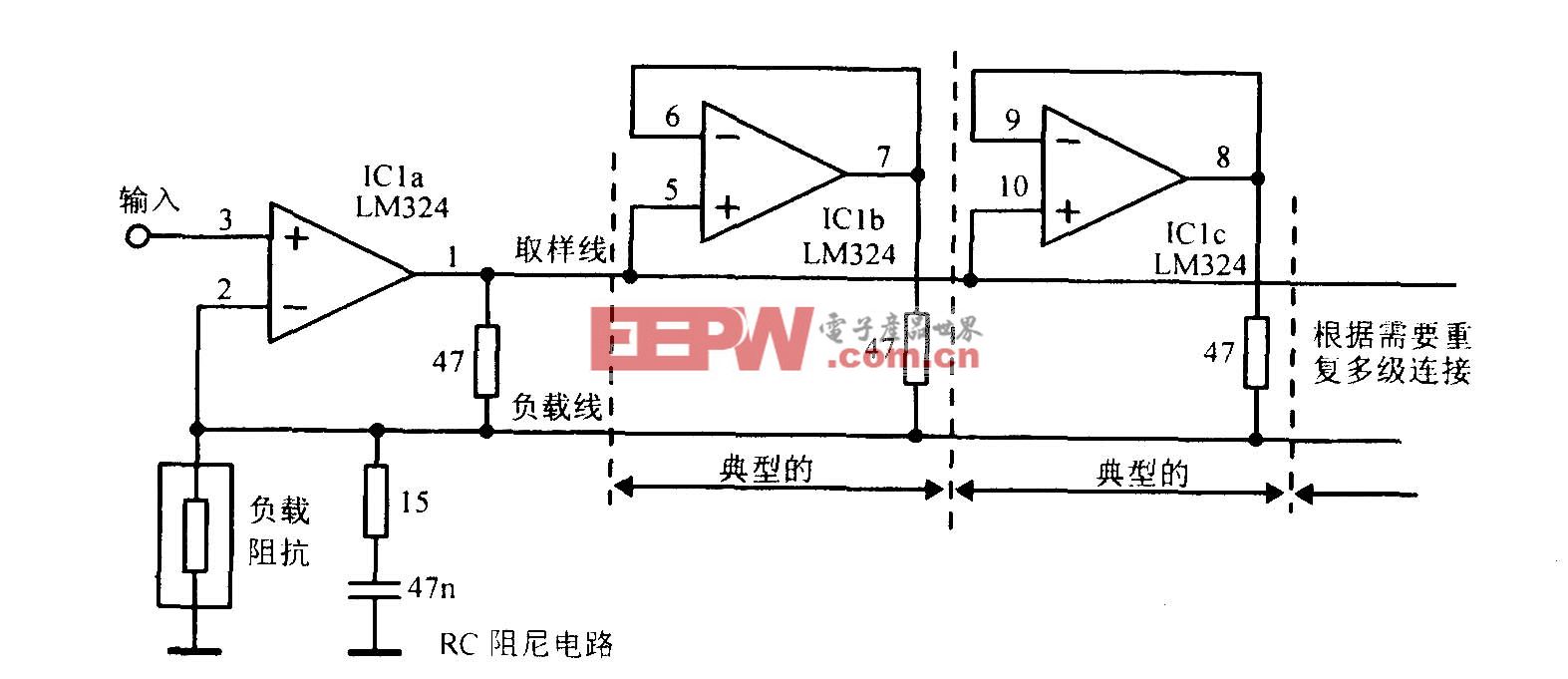

根據SDA(安全數字協會)規范,一條SD總線只能支持一個SD器件。時鐘引腳可以共用,但DAT[3:0]和CMD線則必須由每個SD器件獨占,如圖2所示。

圖2 SD系統總線拓撲結構

此參考設計完全符合SDA規范。下面介紹當使用只有一條總線的控制器支持任意數量的SD 器件時如何滿足上述要求。

CPLD設計

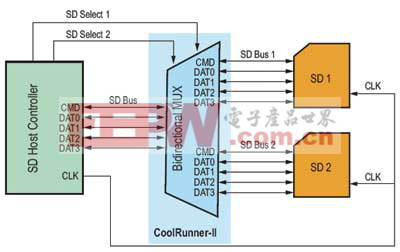

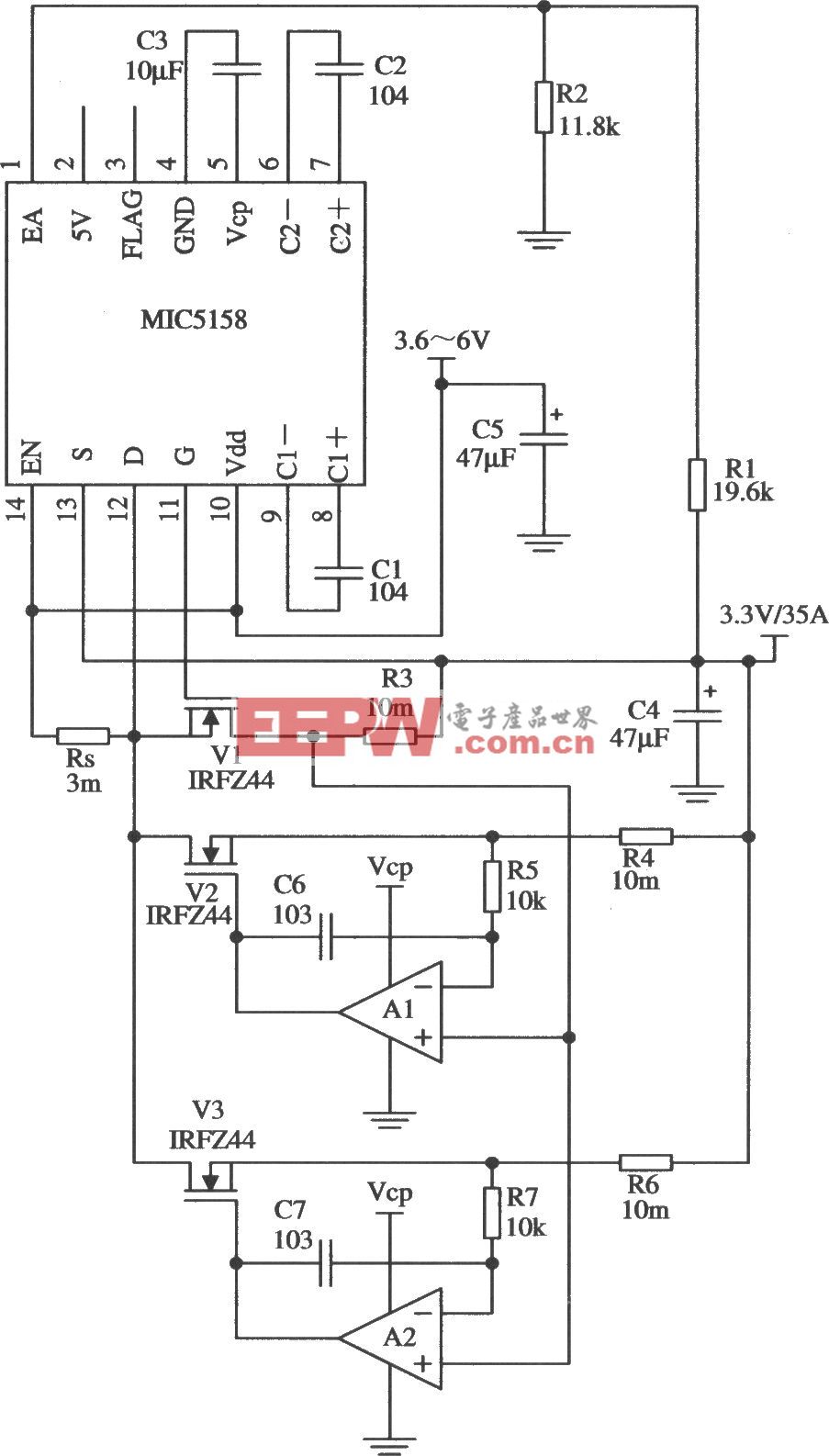

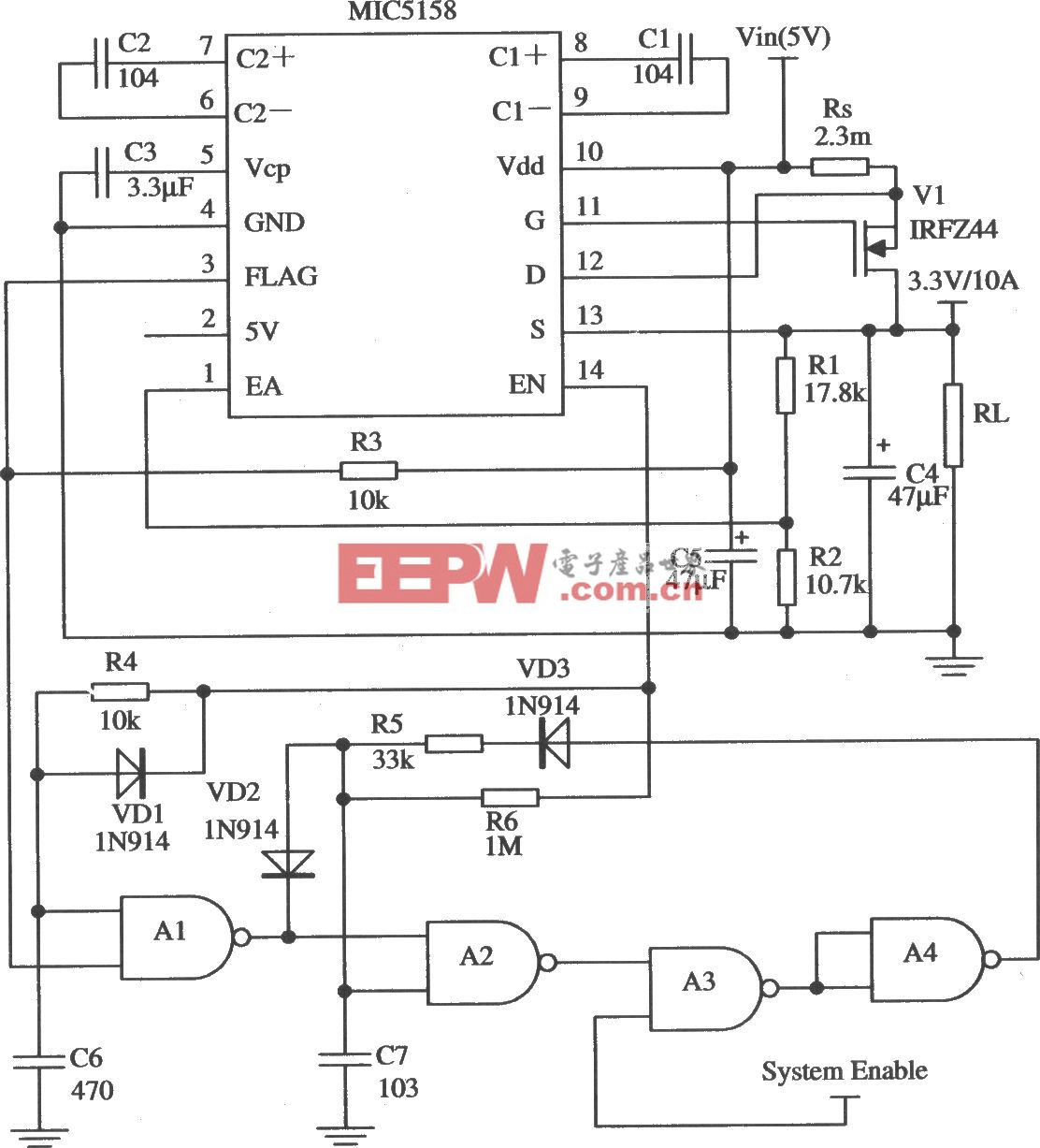

圖 3 所示為用此設計實現兩個SD器件共用同一SD主機接口時的典型用法。從概念上講,可以將這種設計視為和用作雙向多路復用器。主機器件通過“選擇”信號控制CPLD,從而指示與哪個SD器件通信。一旦選中某個SD器件,CPLD器件中的邏輯便自動檢測數據流的方向,并且讓數據相應流動(從主機器件流向SD卡,或者從SD卡流向主機器件)。此設計不需要方向控制引腳,因此使用方便。

圖3 模塊級圖:雙向多路復用器

當多路復用器相應切換時,主機器件可分別訪問各SD器件,而不會影響另一SD器件的狀態。如果主機器件和SD器件都未驅動數據,則CPLD讓系統處于默認的呈弱上拉狀態的高阻抗。此電路的主要用途是加強主機器件的SD能力,但也可用此電路提供電平轉換和/或邏輯隔離。

實現細節

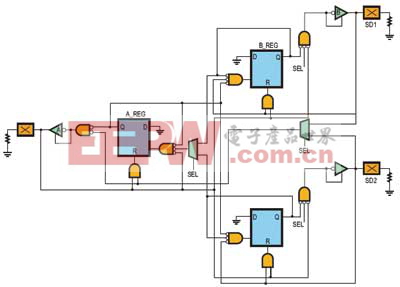

圖4所示為1:2雙向多路復用器設計的實際邏輯電路,該設計可用VHDL語言描述。在初始或空閑狀態下,主機器件和SD卡應處于呈弱上拉狀態的高阻抗。因此,圖4中的電路設計成對 CPLD的輸出緩沖器進行三態控制,從而使外部上拉電阻起作用。寄存器A (A_REG)和寄存器B (B_REG)都設計成在上電時初始化為邏輯“0”。

圖4 兩個SD器件的SD多路復用器電路

通過向 CPLD 輸入“選擇”信號來選擇SD卡。當“選擇”信號為邏輯“0”時選擇SD1,而當“選擇”信號為邏輯“1”時選擇SD2器件。為電路敘述簡明起見,我們假設在以下討論中主機器件只選擇與SD1通信。

此設計的自動方向控制方面的實現方式為:當主機器件與SD1器件二者之一置為低時啟動事務。例如,如果主機器件準備向 SD1 器件傳送數據,則主機器件通過將A側置為低來開始傳送。在置為低時,電路中的邏輯檢測到置低的下降沿,并且通過啟用“B”輸出緩沖器置為有效來響應,而“A”輸出緩沖器仍保持無效狀態。尤其是當A置為低時,會向A_REG的時鐘輸入傳送一個上升沿。繼時鐘控制之后,A_REG的Q輸出變為邏輯“1”,從而阻止B_REG接收時鐘控制事件。當A變為低時,邏輯門B1在A_REG時鐘控制與觸發的同時輸出一個邏輯“1”。這樣便可啟用“B”輸出緩沖器,而B最終會跟隨A置為低。

反之,當A從低轉為高時,邏輯門B1輸出一個低信號,對B輸出緩沖器進行三態控制。這樣便通過外部上拉電阻強制B變為高。一旦A側和B側都變為高,則A_REG和B_REG 復位到0。此過程無限次重復。當SD1要向主機器件傳送數據時,情況相反。另外,如果主機器件準備與SD2器件通信,則電路的“選擇”信號輸入置為邏輯“1”,其事件順序與上述相似。

設計驗證

1 仿真結果

對于此電路,用ModelSim進行了廣泛的功能和時序仿真,測試激勵已經包括在VHDL 下載中。圖5所示為部分仿真結果。

在圖5的第一部分中,“選擇”信號輸入保持為低。白色虛線指示“弱1”狀態,換言之就是表示上拉狀態。在第一個事務中,主機器件嘗試向SD1傳送數據,SD1隨即響應。緊接著,SD1器件嘗試向主機器件傳送數據,主機器件隨即響應。當“選擇”信號輸入置為低時,會發生類似事件。主機器件向SD2器件傳送數據,然后SD2器件向主機器件傳送數據。

圖5 仿真結果

評論