基于Verilog的順序狀態邏輯FSM的設計與仿真

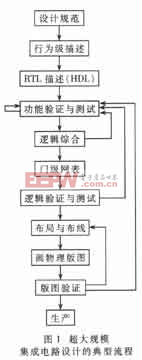

硬件描述語言Verilog為數字系統設計人員提供了一種在廣泛抽象層次上描述數字系統的方式,同時,為計算機輔助設計工具在工程設計中的應用提供了方法。該語言支持早期的行為結構設計的概念,以及其后層次化結構設計的實現。這在設計過程中,進行邏輯結構部分設計時可以將行為結構和層次化結構混合起來;為確認正確性還可以將描述進行模擬,并提供一些用于自動設計的綜合工具。因而Verilog語言為設計者進行大型復雜數字系統的設計提供了途徑。超大規模集成電路設計的典型流程如圖1所示。

本文引用地址:http://www.104case.com/article/152098.htm

本文將以順序狀態邏輯有限狀態機的設計為例介紹用Verilog語言設計數字電路的一般過程。

1 設計規范與設計構思

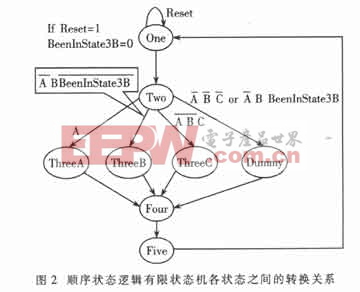

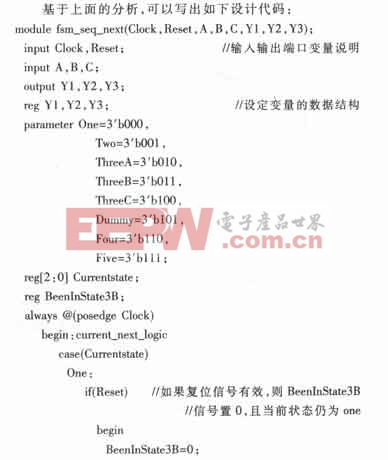

電子設計工程師在設計過程中不可避免地會遇到設計可執行特殊操作序列電路的工作,如用來控制其他電路進行操作的控制器,而有限狀態機(Finite Status Machine,FSM)是設計這種能執行特殊操作序列電路的一種非常有效的模型。FSM的結構通常由當前狀態寄存器、下一狀態邏輯和輸出邏輯三部分構成。FSM也有很多種模型,本文僅以順序狀態邏輯FSM的設計為例來說明用Verilog進行集成電路設計的一般設計過程。為簡單起見,本設計只設計了包含有8個狀態的順序狀態邏輯FSM。8個狀態分別為One、Two、ThreeA、ThreeB、ThTeeC、Dummy、Four、Five。開始狀態為One,各狀態之間的轉換關系如圖2所示。

該順序狀態邏輯FSM的功能及要求如下。

(1)同步復位信號Reset至少要維持4個時鐘周期的高電平信號,以保證狀態機進入狀態One。

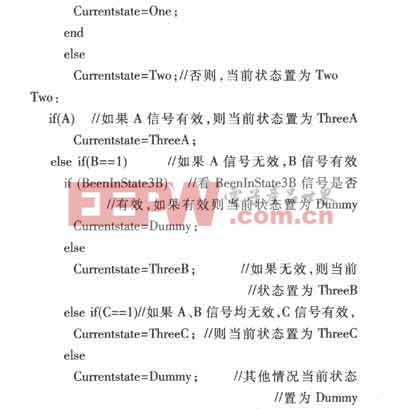

(2)當狀態機在5個狀態中循環時,A、B、C 3個輸入按優先級使狀態機從狀態Two進入相應的狀態ThreeA、ThreeB、ThreeC、Dummy。

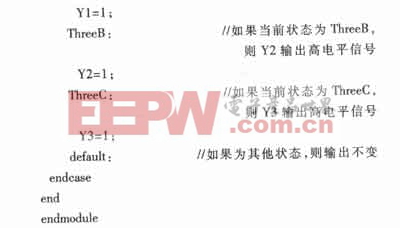

(3)復位后,如果A持續為高電平,則輸出信號Y1的周期為時鐘周期的5倍,且高電平維持的時間為1個時鐘周期。

(4)如果A、B維持為低電平,而C維持為高電平,則輸出信號Y3的周期為時鐘周期的5倍,且高電平維持的時間為1個時鐘周期。

(5)如果A維持低電子,而B維持高電平,則輸出信號Y2與Y1和Y3不同,只維持1個時鐘周期的高電平。因為當狀態機進入狀態ThreeB時,信號BeenInState3B被設置為1,而該信號就會禁止狀態機再次進入狀態ThreeB,直到另一個復位信號出現為止。

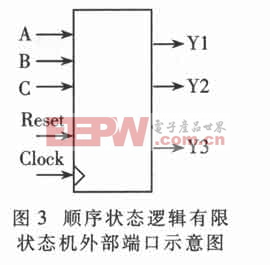

以上是一個時序電路的設計,如何保證正確的時序是設計的關鍵。根據設計要求,該狀態機至少應該有8個端口:5個輸入端口(A、B、C、Reset、Clock),3個輸出端口(Y1、Y2、Y3)。其中輸入端A、B、C和Reset信號均由時鐘邊緣進行觸發,Reset具有最高的優先權,而輸入信號A、B、C的優先權則依次遞減。

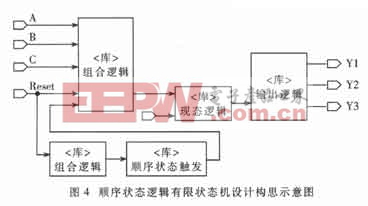

該順序狀態邏輯有限狀態機的端口示意圖和設計構思圖分別如圖3和圖4所示。

2 用Verilog語言編寫源代碼

評論