高速異步FIFO的設計與實現

3 仿真驗證

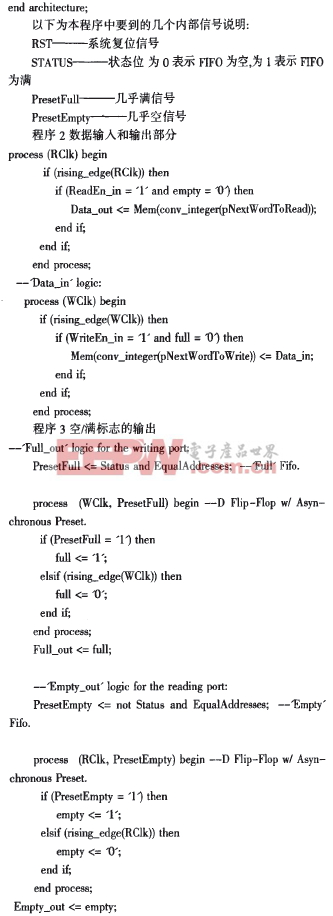

基于以上的分析結合實際本文構造了一個8192x8的FIFO,用MODELSIM進行仿真。對該異步FIFO編寫測試向量進行仿真,如圖2所示。

圖2仿真波形圖

圖2中,WClk為寫時鐘,Writeen_in為寫使能,Full_out為滿信號,Data_in為數據入,RClk為讀時鐘,ReadEn_in為讀時能,Empty_out為空信號,Data_out為數據出,Clear_in為系統清零信號。上面部分為寫地址產生模塊部分的信號波形,從圖2中可以看出.在寫時鐘的上升沿.在寫時能為高有效期間擻據開始輸入到RAM里面,而在讀時鐘的上升沿,在讀時能有效時,在本仿真時間的195ns處.開始輸出數據。將程序下載到LATTICE公司的FPGA芯片中,經過測試驗證,系統的時鐘頻率可達33MHz。

4 總結

本文主要研究了用FPGA芯片實現異步FIFO的一種方法。詳細闡述了空,滿標志信號的產生方法。按照以上思想所設計的異步FIFO已經在實際電路中得到了應用。實踐證明他可以解決大多數異步FIFO電路常見的錯誤。同時增加了系統的可靠性和應用靈活性。

本文作者創新點:通過對FPGA芯片內部EBRSRAM的深入研究.提出了一種利用格雷碼對地址進行編碼的異步FIFO設計方案。實踐證明.增加了系統可靠性和應用靈活性。

評論