基于SoPC的通用在線調試器設計

參數指令傳遞模塊用于合并總線讀寫模塊接收的參數和指令。當寫有效且主控模塊沒有工作時,將從Avalon總線接收的前128位數據拼接起來存放在參數寄存器中,后32位數據由指令寄存器接收;當寫無效時停止輸入,并且啟動狀態機模塊。參數寄存器和指令寄存器均在在本模塊中定義。

狀態機模塊負責仿真JTAG狀態機中的16個狀態,憑借主控模塊中TMS序列驅動實現狀態間的轉移,同時向JTAG的TMS端口送出TMS序列,以控制目標機中JTAG狀態機的運行。在SHIFT_IR和SHIFT_DR狀態下,相應的目標機指令(如ARM指令)和數據通過JTAG的TDI端口送入目標機。

目標機TDO序列接收模塊負責接收目標機傳來的數據,并將其存放在相應的寄存器中。

主控模塊在JTAG狀態機運行之前,根據參數指令傳遞模塊中指令寄存器的值更新狀態機的TMS和TDI序列數據;然后初始化TMS寄存器、TDI寄存器、標志寄存器,通過標志寄存器的值判斷JTAG狀態機的運行;在其運行結束后,在狀態機結束處理子模塊中把目標機傳來的數據送到輸出寄存器,并設置讀有效以啟動總線讀寫模塊。

1.2 JTAG IP core接口程序

在線仿真子系統中,JTAG IP core接口為JTAG IPcore子系統與NiosII CPU硬件環境之間提供數據交互服務。接口程序分成宏定義、寫數據、讀數據3個部分。

宏定義部分,JTAG IP core中的操作指令包括:進入調試狀態、獲取CPU IDCODE、讀/寫寄存器、讀/寫內存、設置斷點、設置觀察點、跳出調試狀態等。

寫數據部分,目標機的內存地址和寄存器號作為參數數據傳遞到JTAG IP core子系統中,調試指令(即宏定義中的指令)與參數一起被寫入JTAG IP core子系統中。部分程序代碼如下:

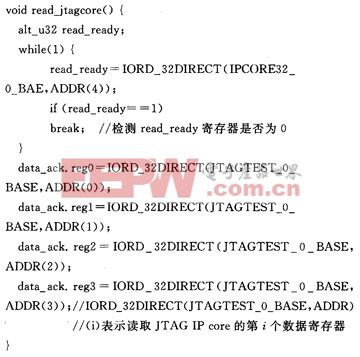

其中,pi表示參數數據(i=0,…,3),ir表示指令。IOWR_32DIRECT(JTAGTEST_0_BASE,ADDR(i),pi)表示將pi或ir的值寫入JTAG IP core。

讀數據部分的功能是從JTAG IP core子系統中讀取目標機傳回的數據。當在線仿真子系統的Nios II CPU準備從JTAG IP core子系統中讀取數據時,JTAG IP core子系統中的寄存器數據不一定是有效數據,因而需設置一個寄存器(命名為read_ready)來循環檢測數據是否有效。如果寄存器的值不為0,則允許讀取數據。

2 JTAG IP core子系統仿真驗證

JTAG IP core子系統設計完成后,為了驗證邏輯的正確性,在QuartusII環境下對該IP core模塊進行了仿真驗證。在仿真中,將NiosII CPU給出的觸發信號cLK修改為2分頻,以便能較直觀地看清觸發子系統允許的TCK信號的產生。當JTAG IP core接口程序被啟動時,總線讀寫模塊開始從Avalon總線上讀取參數和指令(如圖4所示,writedata、address、instOreg_in[0,1,4]及ir寄存器中出現數據)。當參數指令傳遞模塊中的palm和ir寄存器中出現數據后,主控模塊開始工作;同時,主控模塊的busy_flag信號觸發狀態機模塊工作。從圖中可看到,TMS序列出現數據,TDI端口開始送出數據。JTAG IP core模塊能按照預定設計輸出TMS和TDI調試序列,說明該IPcore在邏輯上是正確的。

結 語

本文提出了以知識產權核(即IP core)復用技術為主的通用性調試器設計思路以及實現方法。下一步,可以基于ARM、MIPS系列芯片,結合本文的解決方案實現具體的IP core,同時增加多線程調試等優化工作。

評論