ModelSim+Synplify+Quartus的Altera FPGA的仿真實現

步驟五:設定Device。

※設定Device 為EP1S10F780C6,再按Finish,即可完成Project的設定。

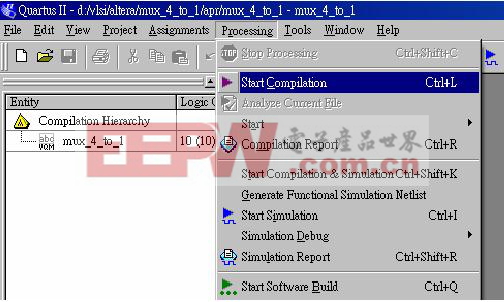

步驟六:編譯。

※點選Processing → Start Compilation,即可開始編譯。

步驟七:完成編譯。

※彈出下面窗口即代表編譯完畢。

以上就是使用Quartus II對電路Netlist做APR的基本流程,并且利用設定仿真工具所產生的xxx.vo(Verilog Output File)與xxx.sdo(Standard Delay Output File)做后仿真。

本文引用地址:http://www.104case.com/article/151781.htm

4、后仿真(Post-Sim)

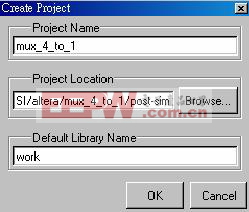

步驟一:啟動ModelSim,然后建立一個Project。

※建立Project的方式為點選File → New → Project…。

※設定Project Name與Project location,按OK即可建立Project。

步驟二:加入設計文檔。

※將xxx.vo更改為xxx.v,然后加入。

步驟三:加入組件庫文件。

※由于我們是采用Altera的Cell Library來合成電路,所以合成后的電Netlist里所包括的那些Logic Gates與Flip-Flop 都是出自于Cell Library,所以模擬時要將此Cell Library加入。

※我們所選用的Family是Stratix,所以到QuartusIIedasim_lib 里將Stratix的Cell Library(stratix_atoms.v)加入。

步驟四:加入測試平臺。

※加入Pre-Sim的測試平臺,并在測試平臺里加上`timescale 1ns/100ps。

步驟五:編譯。

※編譯檔案的方式為點選Compile → Compile All,即可編譯所有的檔案。

※如果編譯時發生錯誤,在顯示錯誤的地方(紅字)點兩下,即可跳到錯誤。

步驟六:仿真。

※仿真文件的方式為點選Simulate → Simulate…。

步驟七:加入要觀察的信號。

※在窗口上按右鍵,然后點選Add → Add to Wave。

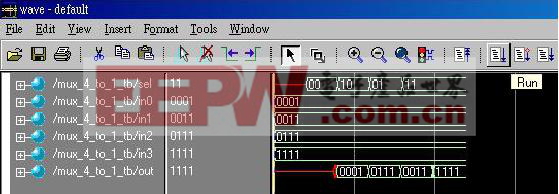

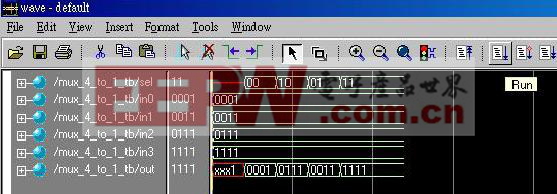

步驟八:觀察波形。

※慢慢看波形吧,沒有波形就沒有真相!

步驟九:比對Pre-Sim 與Post-Sim。

※很明顯地,Post-Sim 的輸出有不穩定的信號,并且受到延遲時間的影響。

評論