基于CPLD器件設計的單穩態電路

(5)電路調試簡單。當需要調整展寬脈沖的寬度時,不需更換元器件,只要將重新設計、仿真通過后的JED熔絲圖文件,通過加載電纜適時加載到CPLD器件內即可。這在對電路進行高、低溫等例行試驗時變得極為簡單、方便和高效。

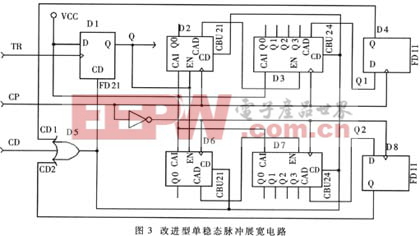

從圖1還可以看出,這種單穩態脈沖展寬電路產生的脈寬精度是小于+或-一個CP時鐘周期。若要提高展寬脈沖寬度的精度,可以采用圖3所示的改進型單穩態脈沖展寬電路,即在圖1電路的基礎上,將進入isp器件的時鐘脈沖信號經反相器反相后,作為另一個相同脈寬控制電路的計數器的時鐘脈沖。

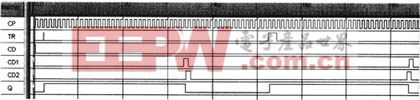

這樣,如果輸入的窄脈沖在時鐘脈沖的前半周期內到達,則由D6、D7、D8組成的脈寬控制電路先開始計數;如果輸入的窄脈沖在時鐘脈沖的后半周期內到達,則由D2、D3、D4組成的脈寬控制電路先開始計數。由于上下兩個脈寬控制電路的時間計數值是相同的,故先計數則先結束,后計數則后結束。兩者之差為半個時鐘周期值。展寬脈沖信號的寬度,始于輸入窄脈沖的前沿,而止于兩個脈寬控制電路中最早結束定時計數的那個計數器的進位脈沖所產生的清零脈沖信號。因此,不管輸入窄脈沖信號的前沿與時鐘脈沖的相對時間關系如何,其輸出展寬脈沖的寬度為脈寬控制電路的時間計數值與輸入窄脈沖的前沿加上時鐘脈沖的前沿或后沿之差。盡管脈寬控制計數電路的時鐘脈沖周期沒有改變,但由于輸入窄脈沖的前沿與控制計數電路時鐘脈沖上升沿的最大時差只有半個時鐘脈沖周期(注意:時鐘脈沖信號的占空比為1:1),故展寬脈沖信號的寬度誤差小于"+"或-半個時鐘脈沖周期。圖4是圖3所示電路的時序仿真波形圖。

這樣,如果輸入的窄脈沖在時鐘脈沖的前半周期內到達,則由D6、D7、D8組成的脈寬控制電路先開始計數;如果輸入的窄脈沖在時鐘脈沖的后半周期內到達,則由D2、D3、D4組成的脈寬控制電路先開始計數。由于上下兩個脈寬控制電路的時間計數值是相同的,故先計數則先結束,后計數則后結束。兩者之差為半個時鐘周期值。展寬脈沖信號的寬度,始于輸入窄脈沖的前沿,而止于兩個脈寬控制電路中最早結束定時計數的那個計數器的進位脈沖所產生的清零脈沖信號。因此,不管輸入窄脈沖信號的前沿與時鐘脈沖的相對時間關系如何,其輸出展寬脈沖的寬度為脈寬控制電路的時間計數值與輸入窄脈沖的前沿加上時鐘脈沖的前沿或后沿之差。盡管脈寬控制計數電路的時鐘脈沖周期沒有改變,但由于輸入窄脈沖的前沿與控制計數電路時鐘脈沖上升沿的最大時差只有半個時鐘脈沖周期(注意:時鐘脈沖信號的占空比為1:1),故展寬脈沖信號的寬度誤差小于"+"或-半個時鐘脈沖周期。圖4是圖3所示電路的時序仿真波形圖。

從時序仿真波形圖中可以看到,前、后兩個輸入窄脈沖的前沿與對應的 展寬脈沖信號的前沿之間的延遲時間是一樣的。而展寬脈沖信號的后沿總是與兩個脈寬控制計數電路中最先結束計數的那個計數器的進位脈沖所產生的清零 脈沖信號相對應的。從而證實了采用圖3所示電路所產生的脈沖信號的寬度精確度較圖1所示之電路幾乎提高一倍。在外部條件不變的情況下,提高展寬脈沖信號精度的方法有多種,這里不再一一例舉。

在CPLD器件中,可以將輸入的窄脈沖展寬;當然,亦可以將輸入的寬脈沖變窄;或使其具有象54HC123單穩態觸發器那樣的延時和可重觸發功能。用CPLD器件可以實現常用單穩態電路的功能;用FPGA器件,同樣可以實現上述功能。采用何種器件何種方法,主要看電路設計的技術指標,設計者所具有的設計環境和周圍電路中所使用器件的類型。總之,隨著大規模集成電路產品性能的不斷提高、體積的不斷減小和成本的不斷降低,基于CPLD器件設計的單穩態電路的性能將大大提高,這種單穩態電路的應用亦將越來越廣泛。

評論