基于CPLD器件設計的單穩態電路

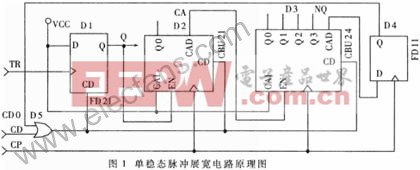

在眾多的CPLD器件中,LatTIce公司在GAL基礎上利用isp技術開發出了一系列ispLSI在線可編程邏輯器件(以下簡稱isp器件),其原理和特點在許多雜志上早有報道,而且國內已有相當多的電路設計人員非常熟悉。Lattice公司的isp器件給筆者印象最深的是其工作的可靠性比較高。圖1即是一種將輸入的窄脈沖信號展寬成具有一定寬度和精度的寬脈沖信號的電路原理圖。

圖中,TR為輸入的窄脈沖雷達信號;CP為輸入的系統時鐘脈沖信號;Q即是單穩態脈沖展寬電路輸出的寬脈沖信號。圖中的單元電路符號D1既是展寬脈沖的前沿產生電路,又是展寬脈沖寬度形成電路;D2、D3是二進制計數器,主要用作展寬脈沖的寬度控制電路。根據對脈沖寬度的不同要求,可以采用不同位數的二進制或其它進制的計數器 (這里,脈沖寬度的設計值是3.2μs,而CP脈沖的周期值是0.1μs);D4是展寬脈沖后沿產生電路,當計數器D3的進位輸出端NQ為"高",且CP脈沖的上升沿到達時,D4輸出端輸出一正向脈沖信號,經D5送至D1的CD清零端,從而結束了一個窄脈沖信號的展寬過程,從D1的Q輸出端輸出一完整的展寬脈沖信號。同時,D5的輸出信號還送至D2、D3的CD清零端,將其清零后,等待下一個窄脈沖的到來。從圖1所示的電路原理圖中可以看到,通常可以將D3的進位輸出信號NQ直接送入D5輸入端,作為D1、D2、D3的清零 脈沖信號。

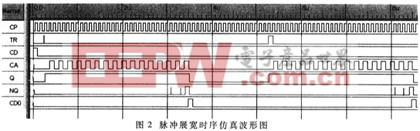

但從圖2所示的時序仿真波形中可以看到,D3的進位輸出NQ波形中,除有正常的進位脈沖信號輸出外,在其前面還有寬度和數量不等的干擾窄脈沖。如果將NQ脈沖經D5后直接作為D1的清零信號,則展寬脈沖的寬度將受干擾窄脈沖的影響而不穩定,因為isp器件中觸發器的清零操作過程是異步進行的。采用D4后,只有與計數時鐘脈沖具有同步關系的那個進位脈沖,才能在D4的輸出端形成清零脈沖。這樣就完全排除了那些干擾窄脈沖的影響,從而保證了展寬脈沖寬度的穩定性和準確性。圖2是這種脈沖展寬的時序仿真波形圖。所用的器件是Lattice公司的ispLSI1032/883-64PIN的PGA封裝器件。

2 基于CPLD器件脈沖展寬電路的特點

從上面的電路原理圖和時序仿真波形圖可以看出,利用isp器件構成的脈沖展寬電路具有如下特點:

(1)對輸入脈沖信號的寬度適應能力較強。最窄可以到ns量級,因其僅與所采用的CPLD器件的工作速度有關。因此,特別適用于對窄脈沖雷達信號進行展寬。

(2)展寬脈沖的寬度可以根據需要任意設定,亦可改變電路(例如與單片機相結合)使其做到現場實時自動加載。

(3)展寬脈沖的寬度穩定、準確。因無外接R、C定時元器件,其脈沖寬度僅與所采用的時鐘頻率和CPLD器件的性能有關。

(4)展寬脈沖的前沿與輸入窄脈沖的前沿之間的延遲時間基本恒定,即這個延遲時間是信號從D1的時鐘輸入端到D1的輸出端Q的延遲時間。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論