基于Max+PlusⅡ平臺的CMI編碼器的設計方案

CMI碼是傳號反轉碼的簡稱,它是一種應用于PCM四次群和光纖傳輸系統中的常用線路碼型,具有碼變換設備簡單、有較多的電平躍變,含有豐富的定時信息,便于時鐘提取,有一定的糾錯能力等優點。

本文引用地址:http://www.104case.com/article/151649.htm在高次脈沖編碼調制終端設備中廣泛應用作接口碼型,在速率低于8 448 Kb/s的光纖數字傳輸系統中也被建議作為線路傳輸碼型。

本文針對光纖通信傳輸碼型的要求和CMI碼的編碼原理,介紹了一種以EPM系列7064芯片為硬件平臺,以Max+PlusⅡ為軟件平臺,以VHDL為開發工具,適合于CPLD實現的CMI編碼器的設計方案。

1 CMI碼的編碼規則

CMI編碼規則如表1所示。

在CMI編碼中,輸入碼字0直接輸出01碼型,較為簡單。對于輸入為1的碼字,其輸出CMI碼字存在兩種結果OO或11碼,因而對輸入1的狀態必須記憶。同時,編碼后的速率增加一倍。

2 CMI編碼器的建模與實現

首先在原始時鐘MUX_Clk的上升沿進行翻轉得到二分頻時鐘Clk,周期為原始時鐘的2倍。

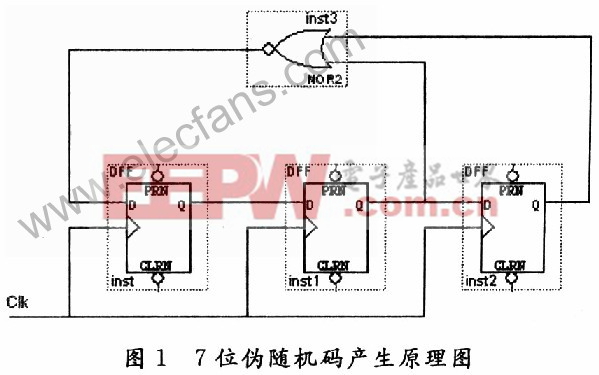

然后產生偽隨機序列,由3個D觸發器產生7位偽隨機序列,序列產生原理如圖1所示。

任何一個D觸發器的輸出都可以作為要產生的m序列,則序列以7為周期循環出現,在3個D觸發器輸出都為0時,語句m_buffer(2)=(m_bu-ffer(1)xor m_buffer(O))Or((not m_buffer(2))and(not m_buffer(1))and(not m_buffer(O))),可以使第一個D觸發器在Clk上升沿到來時輸出為1,從而避免陷入“000的死循環。

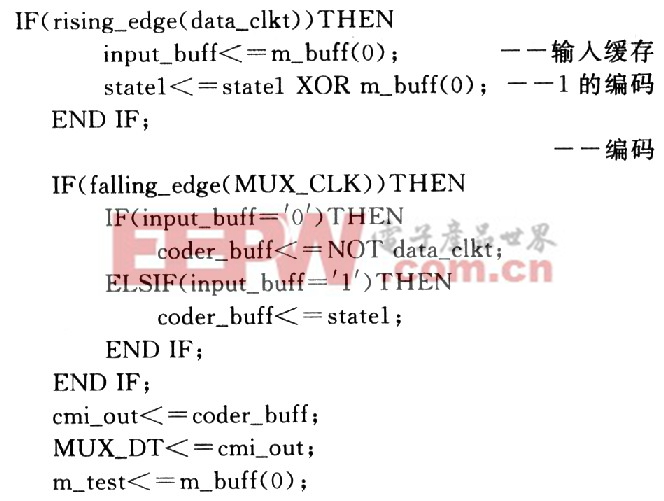

最后為“O”碼、“1”碼的編碼:

“O”編碼的實現:在原始時鐘信號的下降沿對m序列進行檢測,當其值為“0”時,將原始信號的二分頻后的信號求非賦值給編碼輸出,即可實現對“O”進行“01”編碼。

“1”編碼的實現:在原始時鐘信號的二分頻信號的上升沿對m序列進行檢測,如果其值為“1”,用表達式statel=statel X0R m_buff(O)對“1”的奇偶進行記錄;在原始時鐘的下降沿,將statel的值賦給編碼輸出即可實現對“1”的“00”,“11”交替編碼。

評論