基于Xilinx 和FPGA的DDR2 SDRAM存儲器接口控制器的設(shè)計

本白皮書討論各種存儲器接口控制器設(shè)計所面臨的挑戰(zhàn)和 Xilinx 的解決方案,同時也說明如何使用 Xilinx軟件工具和經(jīng)過硬件驗證的參考設(shè)計來為您自己的應(yīng)用(從低成本的 DDR SDRAM 應(yīng)用到像 667 Mb/sDDR2 SDRAM 這樣的更高性能接口)設(shè)計完整的存

本文引用地址:http://www.104case.com/article/151612.htm儲器接口解決方案。

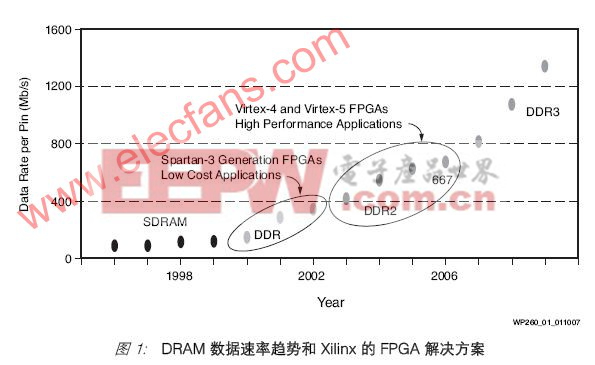

20 世紀 90 年代后期,存儲器接口從單倍數(shù)據(jù)速率 (SDR) SDRAM 發(fā)展到了雙倍數(shù)據(jù)速率 (DDR) SDRAM,而今天的 DDR2 SDRAM 運行速率已經(jīng)達到每引腳 667 Mb/s或更高。當今的趨勢顯示,這些數(shù)據(jù)速率可能每四年增加一倍,到 2010 年,隨著DDR3 SDRAM 的出現(xiàn),很可能超過每引腳 1.2 Gb/s。見圖1。

應(yīng)用通常可分為兩類:一類是低成本應(yīng)用,降低器件成本為主要目的;另一類是高性能應(yīng)用,首要目標是謀求高帶寬。

運行速率低于每引腳 400 Mb/s 的 DDR SDRAM 和低端 DDR2 SDRAM 已能滿足大多數(shù)低成本系統(tǒng)存儲器的帶寬需求。對于這類應(yīng)用,Xilinx 提供了 Spartan-3 系列FPGA,其中包括 Spartan-3、Spartan-3E 和 Spartan-3A 器件。

高性能應(yīng)用把每引腳 533 和 667 Mb/s 的 DDR2 SDRAM 這樣的存儲器接口帶寬推到了極限;對于這類應(yīng)用,Xilinx 推出了 Virtex-4 和 Virtex-5 FPGA,能夠充分滿足今天大多數(shù)系統(tǒng)的最高帶寬需求。

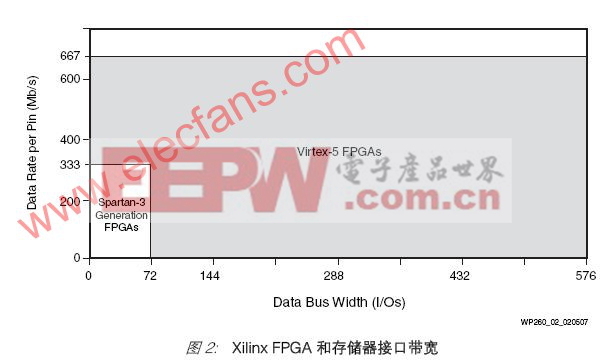

帶寬是與每引腳數(shù)據(jù)速率和數(shù)據(jù)總線寬度相關(guān)的一個因素。Spartan-3 系列、Virtex-4、Virtex-5 FPGA 提供不同的選項,從數(shù)據(jù)總線寬度小于 72 位的較小的低成本統(tǒng),到576 位寬的更大的 Virtex-5 封裝(見圖2)。

高于 400 Mb/s 速率的更寬總線使得芯片到芯片的接口愈益難以開發(fā),因為需要更大的封裝、更好的電源和接地-信號比率。Virtex-4 和 Virtex-5 FPGA 的開發(fā)使用了先進的稀疏鋸齒形 (Sparse Chevron) 封裝技術(shù),能提供優(yōu)良的信號-電源和接地引腳比率。每個 I/O 引腳周圍都有足夠的電源和接地引腳和板,以確保良好的屏蔽,使由同步交換輸出 (SSO) 所造成的串擾噪音降到最低。

低成本存儲器接口

今天,并不是所有的系統(tǒng)都在追求存儲器接口的性能極限。當?shù)统杀臼侵饕臎Q定因素,而且存儲器的比特率達到每引腳 333 Mb/s 已經(jīng)足夠時,Spartan-3 系列 FPGA配之以 Xilinx 軟件工具,就能提供一個易于實現(xiàn)、低成本的解決方案。

基于 FPGA 設(shè)計的存儲器接口和控制器由三個基本構(gòu)建模塊組成:讀寫數(shù)據(jù)接口、存儲器控制器狀態(tài)機,以及將存儲器接口設(shè)計橋接到 FPGA 設(shè)計的其余部分的用戶界面(圖3)。這些模塊都在 FPGA 資源中實現(xiàn),并由數(shù)字時鐘管理器 (DCM) 的輸出作為時鐘來驅(qū)動。在 Spartan-3 系列實現(xiàn)中,DCM 也驅(qū)動查找表 (LUT) 延遲校準監(jiān)視器(一個確保讀數(shù)據(jù)采集具有正確時序的邏輯塊)。延遲校準電路用來選擇基于 LUT 的延遲單元的數(shù)量,這些延遲單元則用于針對讀數(shù)據(jù)對選通脈沖線 (DQS) 加以延遲。延遲校準電路計算出與 DQS 延遲電路相同的一個電路的延遲。校準時會考慮所有延遲因素,包括所有組件和布線延遲。

用戶界面是一種握手型的界面。用戶發(fā)出一條讀或?qū)懨睿绻菍懨畹脑掃€包括地址和數(shù)據(jù),而用戶界面邏輯以 User_cmd-ack 信號回應(yīng),于是下一條命令又可發(fā)出。

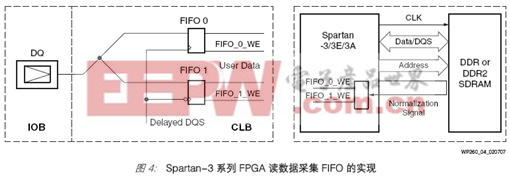

在 Spartan-3 系列實現(xiàn)中,使用可配置邏輯塊 (CLB) 中的 LUT 來實現(xiàn)讀數(shù)據(jù)采集。在讀事務(wù)過程中,DDR 或 DDR2 SDRAM 器件將讀數(shù)據(jù)選通脈沖 (DQS) 及相關(guān)數(shù)據(jù)按照與讀數(shù)據(jù) (DQ) 邊沿對齊的方式發(fā)送給 FPGA。在高頻率運行的源同步接口中采集讀數(shù)據(jù)是一項頗具挑戰(zhàn)性的任務(wù), 因為數(shù)據(jù)在非自由運行 DQS 的每個邊沿上都會改變。讀數(shù)據(jù)采集的實現(xiàn)使用了一種基于 LUT 的 tap 延遲機制。DQS 時鐘信號被適量延遲,使其放置后在讀數(shù)據(jù)有效窗口中具有足夠的余量,以在 FPGA 內(nèi)被采集。

讀數(shù)據(jù)的采集是在基于 LUT 的雙端口分布式 RAM 中完成的(見圖4)。LUT RAM 被配置成一對 FIFO,每個數(shù)據(jù)位都被輸入到上升邊沿 (FIFO 0) 和下降邊沿 (FIFO 1)的FIFO 中,如圖4 所示。這些深度為 16 個輸入的 FIFO 異步運行,具有獨立的讀寫端口。

來自存儲器的讀數(shù)據(jù)寫到經(jīng)過延遲的 DQS 上升邊沿的 FIFO_0 中,并寫到經(jīng)過延遲的DQS 下降邊沿的 FIFO_1 中。將讀數(shù)據(jù)從 DQS 時鐘域傳輸?shù)酱鎯ζ骺刂破鲿r鐘域就是通過這些異步 FIFO 完成的。在存儲器控制器的時鐘域中,可以從 FIFO_0 和FIFO_1 同時讀出數(shù)據(jù)。FIFO 的讀指針在 FPGA 的內(nèi)部時鐘域中生成。寫使能信號(FIFO_0 WE 和 FIFO1_WE)的生成通過 DQS 和一個外部回送(亦即歸一化)信號完成。外部歸一化信號作為輸出傳送至輸入/ 輸出模塊 (IOB),然后通過輸入緩沖器作為輸入取出。這種技術(shù)可補償 FPGA 與存儲器器件之間的 IOB、器件和跡線延遲。從FPGA 輸入管腳發(fā)出的歸一化信號在進入 LUT 延遲電路之前使用與 DQS 相似的布線資源,以與布線延遲相匹配。環(huán)路之跡線延遲應(yīng)為發(fā)送給存儲器的時鐘和 DQS 之跡線延遲的總和(圖4)。

寫數(shù)據(jù)命令和時序由寫數(shù)據(jù)接口生成并控制。寫數(shù)據(jù)接口使用 IOB 觸發(fā)器和 DCM 的90 度、180 度和 270 度輸出,發(fā)送按照 DDR 和 DDR2 SDRAM 的時序要求與命令位和數(shù)據(jù)位正確對齊的 DQS。

用于 Spartan-3 系列 FPGA 的一種 DDR 和 DDR2 SDRAM 存儲器接口實現(xiàn)已通過硬件進行了充分驗證。一個利用 Spartan-3A 入門套件的低成本 DDR2 SDRAM 參考設(shè)計示例已完成。此設(shè)計為板上 16 位寬 DDR2SDRAM 存儲器器件而開發(fā),并使用了XC3S700A-FG484。此參考設(shè)計僅利用了 Spartan-3A FPGA 器件可用資源的一小部分:13% 的 IOB、9% 的邏輯 Slice、16% 的 BUFG MUX 和八個 DCM 中的一個。這一實現(xiàn)為其余部分 FPGA 設(shè)計所需的其他功能留下了可用資源。

使用存儲器接口生成器 (MIG) 軟件工具(本白皮書后面的部分有說明),設(shè)計人員可以很容易地定制 Spartan-3 系列的存儲器接口設(shè)計,以適合自己的應(yīng)用。

高性能存儲器接口

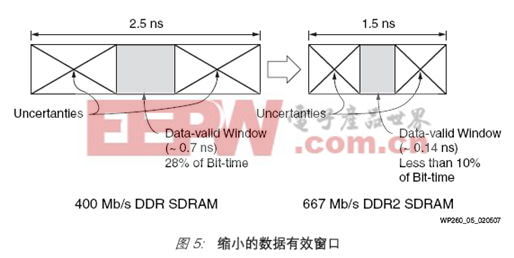

隨著數(shù)據(jù)速率的提高,滿足接口時序方面的要求變得愈益困難了。與寫入存儲器相比,從存儲器中讀數(shù)據(jù)時,存儲器接口時鐘控制方面的要求通常更難滿足。追求更高數(shù)據(jù)速率的趨勢使得設(shè)計人員面臨巨大挑戰(zhàn),因為數(shù)據(jù)有效窗口(此為數(shù)據(jù)周期內(nèi)的一段時間,其間可獲得可靠的讀數(shù)據(jù))比數(shù)據(jù)周期本身縮小得快。造成這種情況的原因是,影響有效數(shù)據(jù)窗口尺寸大小的系統(tǒng)和器件性能參數(shù)具有種種不確定性,它們縮小的速率與數(shù)據(jù)周期不同。

如果比較一下運行速度為 400 Mb/s 的 DDR SDRAM 數(shù)據(jù)有效窗口和運行速度為 667Mb/s 的 DDR2 存儲器技術(shù),這種情況就一目了然了。數(shù)據(jù)周期為 2.5 ns 的 DDR 器件擁有 0.7 ns 的數(shù)據(jù)有效窗口,而數(shù)據(jù)周期為 1.5 ns 的 DDR2 器件僅有 0.14 ns 的數(shù)據(jù)有效窗口(圖5)。

顯然,數(shù)據(jù)有效窗口的加速減損給 FPGA 設(shè)計人員帶來了一堆全新的設(shè)計挑戰(zhàn),要創(chuàng)建和維護可靠的存儲器接口性能,就得采用更有效的方法。

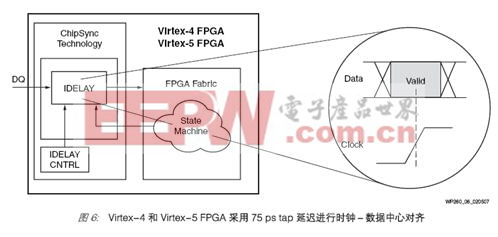

正如 Spartan-3 系列 FPGA 中所實現(xiàn)的那樣,使用讀數(shù)據(jù) DQS 可以把讀數(shù)據(jù)采集到可配置邏輯塊 (CLB) 中,但是使用 LUT 把 DQS 或時鐘與數(shù)據(jù)有效窗口中心對齊時,所用的延遲 tap 卻很粗糙。CLB 中實現(xiàn)的延遲 tap 具有大約幾百微微秒 (ps) 的分辨率,然而,對于超過 400 Mb/s 的數(shù)據(jù)速率的讀取采集時序,所需的分辨率要比基于CLB 的 tap 高一個數(shù)量級。Virtex-4 和 Virtex-5 FPGA 采用 I/O 模塊中的專用延遲和時鐘資源(稱為 ChipSync? 技術(shù))來解決這一難題。內(nèi)置到每個 I/O 中的 ChipSync模塊都含有一串延遲單元(tap 延遲),在 Virtex-4 中稱為 IDELAY,而在 Virtex-5FPGA 中稱為 IODELAY,其分辨率為 75 ps (見圖6)。

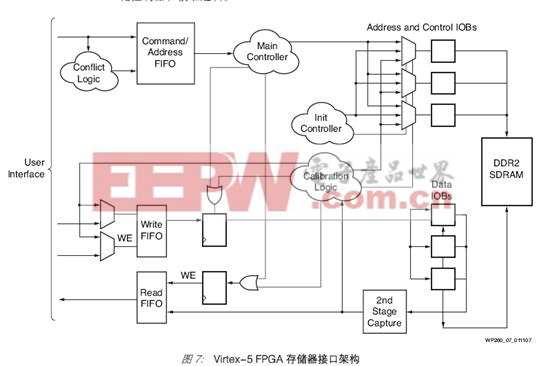

此實現(xiàn)的架構(gòu)基于幾個構(gòu)建模塊。用戶界面負責(zé)把存儲器控制器和物理層接口橋接到其余 FPGA 設(shè)計,它使用 FIFO 架構(gòu)(圖7)。FIFO 有三套:命令/ 地址 FIFO、寫FIFO、讀 FIFO。這些 FIFO 保存著命令、地址、寫數(shù)據(jù)和讀數(shù)據(jù)。主要的控制器模塊控制讀、寫和刷新操作。其他兩個邏輯模塊執(zhí)行讀操作的時鐘-數(shù)據(jù)中心對齊:初始化控制器和校準邏輯。

評論