Spartan-3 FPGA實現的DSP嵌入系統及其在在平板顯示器中的應用

*SelectIO-超級連接本文引用地址:http://www.104case.com/article/151607.htm

每個I/O針腳都支持24個通用I/O標準中的任意一個,所以Spanan-3 FPGA可以最低的成本提供最靈活的連接,即可編程I/O技術;支持PCI、HSTL、SSSL、超傳送(HyperTransport)、LVDS、RSDS、LVPECL、LVPEL、LVCMOS及更多。

2.14邏輯資源

豐富的邏輯單元,寄存器具有移位能力;18X18乘法器;JTAG邏輯與IEEEll49.1/1532說明兼容。

2.15 可以被Xilinx ISE(系統內仿真器)開發系統支持。即綜合、映射、替代和尋址。

Spartan-3設備以最低成本提供高密度的FPGA,這使得它們非常適合于數量大、注重成本、以DSP為核心的應用程序。

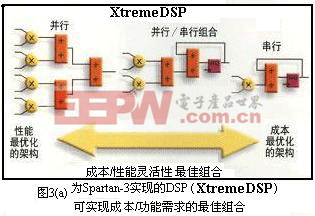

即嵌入式18×18乘法器(最多104個)、每秒最多3300億次乘法和累加運算(MAC/s)、優秀的高速DSP功能的并行實現能力、靈活的串聯架構,可實現成本/功能需求的最佳組合,見圖所示最大的成本/性能靈活性。預驗證的DSP算法和核心,即濾波器、檢波、變換、算法、FEC、相關器。

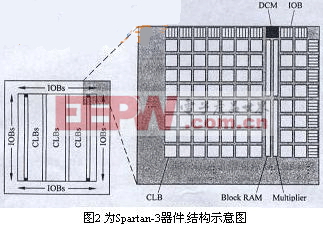

2.2 Spartan-3獨特的器件結構

Spartan-3系列的結構可由5個基本的可編程功能模塊組成,分別是可配置邏輯模塊(CLB),輸入/輸出模塊(IOB)、BlockRAM、乘法器模塊和數字時鐘管理器(DCM)。這些 小模塊的組成如圖2所示。一系列IOB模塊沿芯片的邊沿分布,圍繞著一組按規則排列的CLB模塊。如XC3S50型只有一個按列排列的BlockRAM嵌在陣列中,XC3S200型到XC3S2000小型有兩個按列排列的BlockRAM,而XC3S4000和XC3S5000有4個BlockRAM。每個列狀BLockRAM是由幾個18kbRAM模塊組成,每個模塊與專用乘法器有受.。DCM放在BLockRAM的外端。

由上所見, FPGA解決方案的可編程特性降低了新系統設計的內在開發風險。由于擁有諸如多個I/O槽、片上數字時鐘管理器、以及大量的Block存儲器和分布式存儲器等其它功能,Spartan-3也可以高效實現許多控制/膠合邏輯功能,有效減小了系統的尺寸、復雜度和成本。

2.3 Spartan-3 FPGA來實現的DSP嵌入系統

Spartan-3設備以最低成本提供高密度的FPGA,這使得它們非常適合于數量大、注重成本、以DSP為核心的應用程序。

其嵌入式18×18乘法器(最多104個)、每秒最多3300億次乘法和累加運算(MAC/s)、優秀的高速DSP功能的并行實現能力、靈活的串聯架構,可實現成本/功能需求的最佳組合,見圖3(a)所示最大的DSP成本/性能靈活性。

預驗證的DSP算法和核心,即濾波器、檢波、變換、算法、FEC、相關器。而Spartan-3 FPGA 在高性能DSP應用中,有各種不同FIR濾波器技術的適用情況,而FIR濾波器的算法為:

公式中n個系數與n個相應的數據采樣相乘,再對內積求和產生單個結果。系數數值將確定濾波器的低通/高通/帶通特性,可以利用不同的架構和不同的方法來實現濾波器的功能。

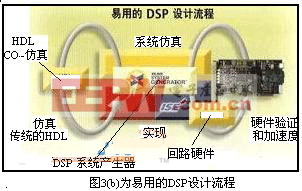

由此可以說,因為FPGA是極高并行度的信號處理引擎,能夠滿足算法復雜度不斷增加的應用要求,通過并行方式提供極高性能的信號處理能力。Xilinx的XtremeDSP模塊,如圖3(b)所示,使得Sparten3系列FPGA可以為高性能的數字信號處理提供理想的解決方案,達到傳統上由ASIC或ASSP完成的高性能信號處理能力。可以針對數字通信和視頻圖象處理等應用開發高性能的DSP引擎,也可在可編程DSP系統中作為預處理器或協處理器等。

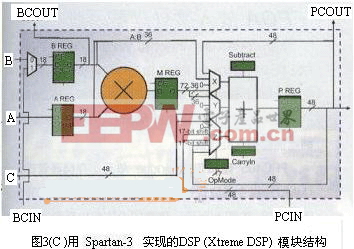

由于嵌入式18×18乘法器(最多104個)適應DSP應用中的眾多的功能。提高了操作數輸入、中間積和累加器輸出的可編程流水線操作。

在復雜算法的數字處理系統中,系統要求的不斷提高和集成規模的不斷擴大,使得系統結構在設計的開始階段是不明確的,不可能直接用RTL(寄存器轉移級)設計方法進行描述,所以將系統集成到數字芯片中。

采用數字技術對復雜算法進行硬件實現時,首先遇到的問題是在結構上并沒有預先的規定,因此需要首先對算法建模和仿真進行優化。與基于RTL針對結構清晰的設計方法不同,算法設計把焦點從針對結構的細節轉移到對設計的整體要求和行為,在最高的算法層次上考慮如何進行設計,對系統的行為描述定義了設計要執行的算法,不涉及或很少涉及實現細節,因此行為描述比RTL描述要簡潔的多。

圖3(c)為易用的DSP設計流程所示, 糸統產生器的DSP設計環境,包含了系統數學建模、算法優化和改進、設計校驗和診斷及HDL產生和仿真等。而綜合DSP設計服務包括DSP設計等級、現埸工程服務。

評論