用FIFO實現DSP間的雙向并行異步通訊

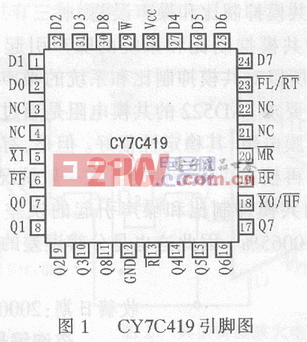

內容摘要:介紹了利用CYPRESS公司的FIFO芯片CY7C419實現DSP間雙向并行異步通訊的方法,該方法簡單實用,速度快,特別適用于小數據量的數據相互傳送。文中給出了CY7C419的引腳功能以及用FIFO實現DSP間雙向并行異步通訊的硬件結構和軟件流程。

本文引用地址:http://www.104case.com/article/151565.htm在多CPU的分布式信號處理系統中,往往涉及CPU間的通訊與數據交換,大數據量的數據傳輸一般采用DMA方式,而小數據量的數據交換采用并行接口則比較快速靈活。因此,對于傳輸速度要求較高的DSP間的小數據量的數據交換及通訊來說,要提高DSP的工作效率,不僅要求并行接口的響應快,而且必須采用異步方式以免相互等待。本文介紹了采用CYPRESS公司的FIFO芯片CY7C419來實現DSP間的雙向并行異步通訊接口。該方法不僅比用TTL鎖存器的方式速度快,而且譯碼邏輯簡單,另外,由于FIFO芯片有一定的深度(256個),因此,在少于256個數據傳輸時,可實現零等待時間。

1 FIFO芯片簡介

全滿(FF)和全空(EF)標志用以防止數據溢出或不足;

擴展輸入(XI)、擴展輸出(X0)、首次裝載(FL):用以實現無限的寬度及深度擴展,深度擴展技術可使操縱控制信號從一個元件并行傳至另一個元件,因而消除了傳輸延遲的串行附加,其最高讀、寫速度可達50MHz,讀寫信號低電平有效;

當CY7C419獨立使用或多片實現寬度擴展結構時,半空標志(HF)輸出有效,在深度擴展結構中,該此腳輸出擴展輸出信息(XO)并告知下一個FIFO;

D0~D8為數據輸入,Q0~Q8為數據輸出。

R、W及MR分別為讀、寫及復位信號的輸入端,它們均為低電平有效。

評論