基于SERDES收發器和CPRI的電信系統低延遲變化設計

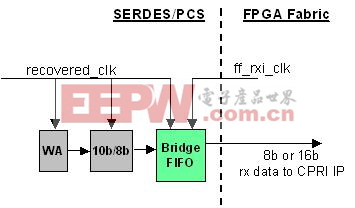

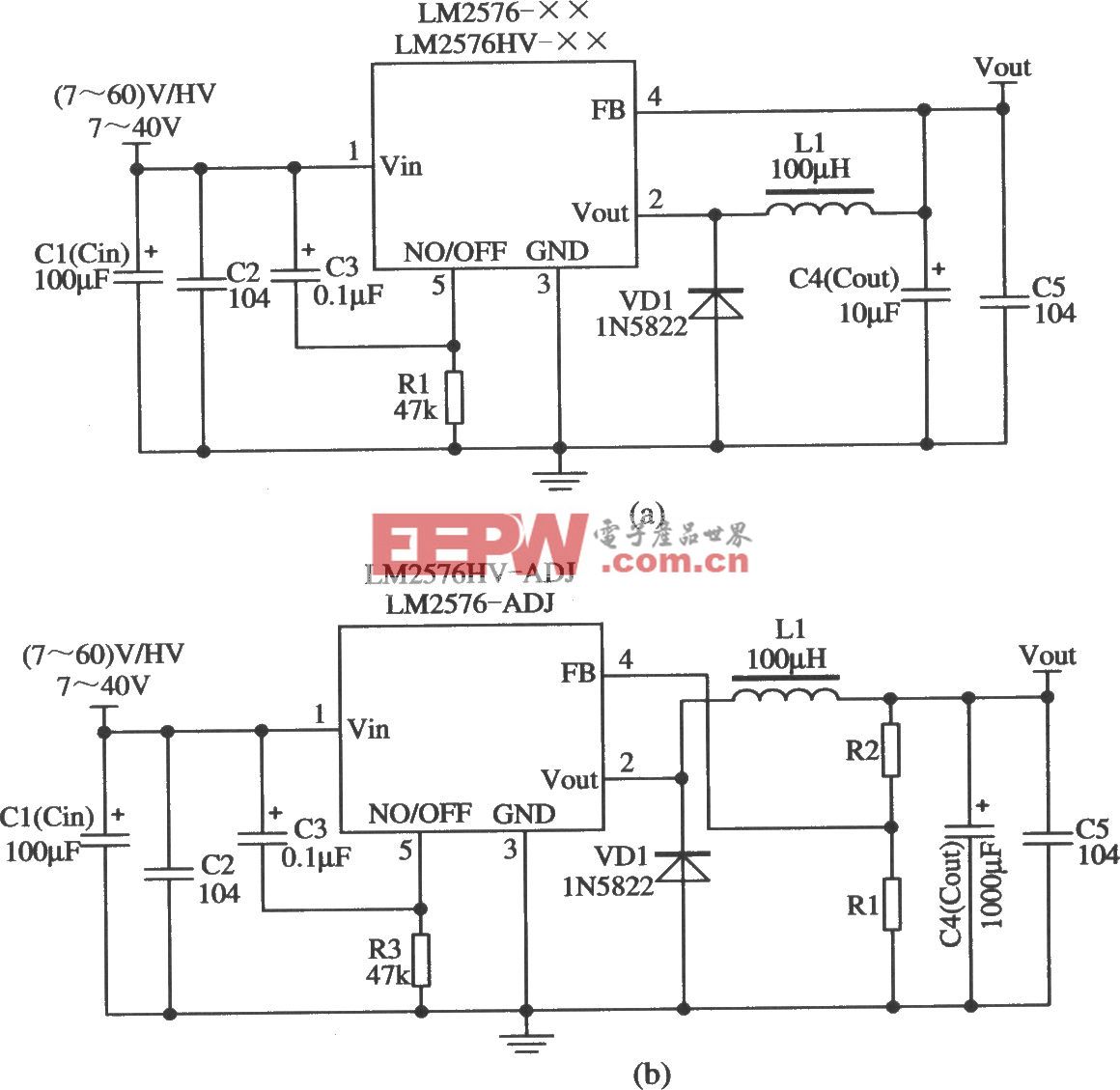

采用基于SERDES的FPGA混合結構,還需要橋接FIFO來支持從高速PCS時鐘到FPGA時鐘域的轉換。通過設計,這個FIFO可導致多達2個并行時鐘周期的延時變化。在2.488Gbps的線速下,PCS并行時鐘以該速率的十分之一運行,時鐘周期大約為4ns。因此,FIFO(TxRx)的每個方向上都有±8ns的最大延遲變化,這導致一共±16ns的延遲變化。

使情況變得更糟糕的是設計者沒有預見到這些延時變化。因此不能在系統級估計和補償這些變化,在支持諸如分集傳輸和GPS服務時,這是主要的問題。

圖4:橋接FIFO導致的延時變化。

針對基于FPGA的傳統嵌入式SERDES/PCS,表1總結了導致整個執行時間發生的主要因素,并與CPRI規范進行了比較。分析這些數目,可很清楚看到字對齊和橋接FIFO對大的延時變化起主要作用,導致超過規范的來回行程延時容忍度。

幸運的是,通過對傳統的實現做一些小的修改就可以解決這個問題。用戶可以繞過嵌入式數字PCS功能,在FPGA中實現這些邏輯。因為現在的邏輯運行在單個FPGA時鐘域中,所以這個方法不再需要橋接FIFO,并且設計者可以訪問導致延時的字對齊電路。在FPGA邏輯里可以通過訪問寄存器的方式來獲得字對齊電路測量到的延遲信息,而從在系統級針對延時變化進行補償。這些補償允許無線頭之間在指定的窗口內進行傳輸以支持前面提到的業務,諸如分集傳輸和GPS。圖5給出了低延遲設計的實現方案,關鍵元件都在FPGA邏輯中實現。

如果采用這個推薦的實現方案,則不再需要導致大的延時變化的單元,即省去了橋接FIFO。可訪問字對齊電路的寄存器使用戶能計算并進行系統級補償,以確保不同無線頭的傳輸都在規定的時序窗內進行。當然,模擬SERDES和CPRI IP,或者設計本身仍然存在延時,但此時整個配置的精確度已得到大大改善,可以在多跳應用中使用。該方案占用的器件資源很小,新的模塊只需幾百個LUT。表2列出了這個配置中新的延時變化。可以看到總的延時變化大大下降。對單跳來說這很容易滿足來回行程延時規范,對支持多達4級的多跳應用是足夠的低。

圖5:低延遲設計的實現方案,其中關鍵元件都在FPGA邏輯中實現。

使用FPGA的另外一些優點

許多年來FPGA是無線工業獲得成功的一部分。從簡單的粘合邏輯功能和基帶濾波器到更復雜的功能,例如在如今RRH設計中所需要的數字上變頻、數字下變頻、峰值因子衰減和數字預失真,充分利用了FPGA的靈活性和產品快速上市的優點。嵌入式DSP塊、嵌入式存儲器和高速串行I/O(SERDES)的特性與無線設備供應商的新需求需要完美地吻合。隨著可實現CPRI功能的低成本器件的引進,例如LatticeECP2M FPGA系列,基站設計者有了有力的杠桿,在可編程平臺上集成了系統級的功能,還有除了技術功能以外的關鍵因素:低成本、低功耗和小的器件尺寸。

本文小結

遠程基站拓撲結構在功耗、部署的靈活性、更小的固定面積,以及更低的CAPEX和OPEX方面系統供應商提供了許多優點。一個集成和靈活的低成本平臺能滿足新興且不斷變化的規范非常關鍵,低成本FPGA對滿足這些需要是理想的選擇。對基于FPGA的CPRI實現用于RRH拓撲結構有一些批評意見,主要是說它們不能夠符合CPRI所要求的精確鏈接規范。本文說明了事實并非如此,事實上,甚至可以輕松地支持多跳RRH拓撲結構。因此,可編程低功耗解決方案且非常誘人的價格是下一代BTS開發是最好的方法。

評論