FPGA設(shè)計中的時序管理

當(dāng)

二、導(dǎo)言

FPGA的設(shè)計與高速接口技術(shù)可以幫助你滿足今天的市場要求,但也提出了一些有趣的設(shè)計挑戰(zhàn)。為了確保存儲器接口的數(shù)據(jù)傳輸準(zhǔn)確,在超過200兆赫茲以上,進(jìn)行時序分析將發(fā)揮更突出的作用,以識別和解決系統(tǒng)運行的問題。在這些頻率內(nèi),最重要的是創(chuàng)建和控制時序空余,留下最小的空余,以確保數(shù)據(jù)采集和演示窗口的準(zhǔn)確。更快的邊緣速率同時也放大物理設(shè)計的影響,造成信號完整性問題,對此則需要更多的沉降時間及縮小時序空余。歡迎轉(zhuǎn)載,本文來自電子發(fā)燒友網(wǎng)(http://www.elecfans.com )

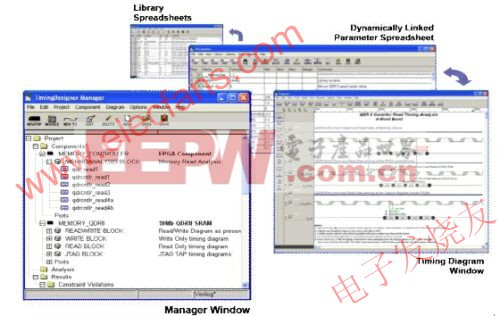

FPGA器件現(xiàn)在還包括某些先進(jìn)的功能,如支持帶有I/O單元接口的雙通道數(shù)據(jù)(DDR)和板上鎖相環(huán)(PLL)網(wǎng)絡(luò)進(jìn)行精確時鐘控制等等。這些在FPGA技術(shù)中的高級功能均提供先進(jìn)的接口模塊,從而有助于減少界面設(shè)計,再加上TimingDesigner軟件的獨特能力,在最短的時序中提供最準(zhǔn)確、有力的解決方案。本文主要探討了DDR型存儲器接口設(shè)計中必要的時鐘偏移及數(shù)據(jù)采集的時序空余。

圖1:TimingDesigner軟件便于捕獲設(shè)計特點的圖形界面窗口。

三、DDR/QDR存儲器接口的設(shè)計問題

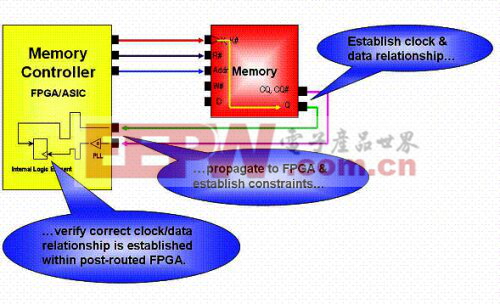

DDR或四倍數(shù)據(jù)速率(QDR)存儲設(shè)備可以提供和接受兩倍于器件時鐘頻率的源同步數(shù)據(jù),這意味著數(shù)據(jù)在時鐘的上升緣和下降緣傳輸。此外,需要捕捉時鐘偏移和進(jìn)行適當(dāng)?shù)卣{(diào)整,以確保適當(dāng)?shù)臅r鐘與數(shù)據(jù)關(guān)系。

如前所述,現(xiàn)在一些FPGA裝置包括DDR接口的I/O單元和板上的PLL網(wǎng)絡(luò)。這意味著,你必須有一個方式來控制模塊的準(zhǔn)確和可靠。為了說明這一點,讓我們來讀取QDR II SRAM源同步接口的設(shè)計要求看看實例。

在同步存儲器系統(tǒng)例如QDR SRAM中,數(shù)據(jù)是與時鐘同步的,所以存儲器數(shù)據(jù)的相位必須旋轉(zhuǎn)90度。這種相位旋轉(zhuǎn)通常在有效數(shù)據(jù)窗口中進(jìn)行時鐘中心調(diào)整,這是QDR實現(xiàn)準(zhǔn)確數(shù)據(jù)采集的一個重要設(shè)計特點(見下文圖2)。如果要改變時鐘中心,我們可以通過對板上FPGA的PLL網(wǎng)絡(luò)進(jìn)行簡單的延時時鐘信號來達(dá)到。

圖2:中心對齊的時鐘/數(shù)據(jù)關(guān)系。

獲取數(shù)據(jù)

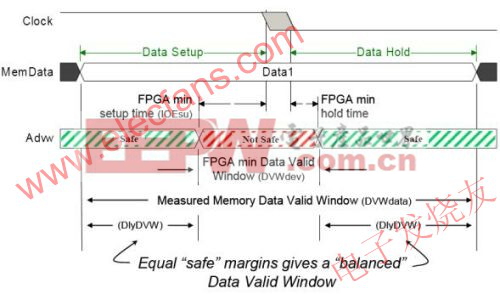

延遲時鐘信號可以實現(xiàn)中心對齊以避免各種溫度變化和其他類似的設(shè)計影響,可能會對時鐘或數(shù)據(jù)方面帶來一些影響,但不會很大,但違背了接收存儲器的建立或保持時序的要求。在理論上,對于大部分器件,中心對齊的時鐘邊緣將最大限度地建立和保持時序,留出足夠的安全空余。然而,除非建立的需求合適于保持的需求,時鐘信號的中心對齊將提供更多的時序空余。

理想的解決辦法是為器件的建立和保持提供一個最大的安全空余,可以通過轉(zhuǎn)化平衡空余,為二者都提供相同的安全空余。為了平衡空余,我們?yōu)榻邮掌骷_定最低的有效數(shù)據(jù)窗口,在實際有效數(shù)據(jù)窗口的中心窗內(nèi)可以給我們的存儲器提供設(shè)計參數(shù)。

利用接收器件最小的建立和保持時間,我們可以利用下面的公式確定最小的安全的有效數(shù)據(jù)窗口:

最小創(chuàng)建時間+最低保持時間=最低有效數(shù)據(jù)窗口

如圖3所示,在存儲器器件中可以看出,實際結(jié)果是在有效數(shù)據(jù)窗口中間。為了確保獲取數(shù)據(jù),總線必須在接收器最小的有效數(shù)據(jù)窗口外的安全區(qū)域內(nèi)進(jìn)行轉(zhuǎn)換。根據(jù)時鐘與數(shù)據(jù)的關(guān)系,信號設(shè)計在任一區(qū)域內(nèi),在獲取數(shù)據(jù)時,我們確保盡可能多的安全空余。

圖3:平衡實際有效數(shù)據(jù)窗口中的最小有效數(shù)據(jù)窗口。

實現(xiàn)適當(dāng)?shù)臅r鐘偏移

源同步時鐘的相位偏移將有效地改變存儲控制器接收寄存器的最小有效數(shù)據(jù)窗口,因此將形成平衡有效數(shù)據(jù)窗口。時鐘偏移調(diào)整是FPGA裝置中PLL器件的一個組成部分。要確定偏移的值,我們必須考慮到影響信號的布線延遲和任何外部延遲。

評論