短幀Turbo譯碼器的FPGA實現

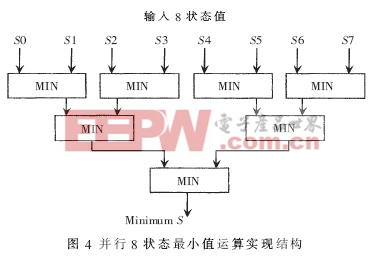

3.4 8狀態值最小值運算單元

由MAX-LOG-MAP算法可知,在進行前后向遞推歸一化處理和計算譯碼軟輸出時,均需要計算每一時刻8個狀態的最小值。為了減小計算延時,采用了8狀態值并行比較的結構,與串行的8狀態值比較結構相比較,要少4級延時。實現結構如圖4所示。

4 仿真結果

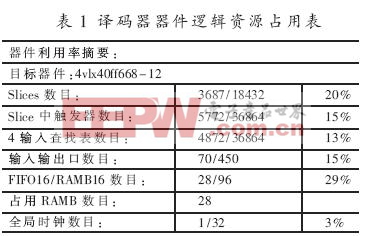

按照以上所分析的簡化譯碼算法、FPGA實現的相關參數和結構,整個譯碼采用Verilog HDL語言編程,以Xilinx ISE 7.1i、Modelsim SE 6.0為開發環境,選定Virtex4芯片xc4vlx40-12ff668進行設計與實現。整個譯碼器占用邏輯資源如表1所示。

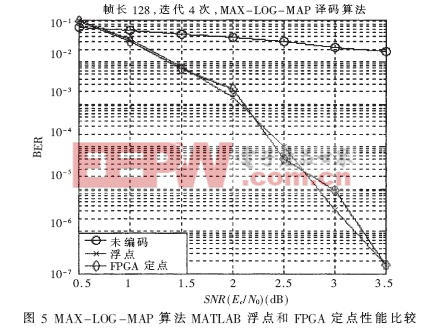

MAX-LOG-MAP譯碼算法,幀長為128,迭代4次的情況下,MATLAB浮點算法和FPGA定點實現的譯碼性能比較如圖5所示。

由MAX-LOG-MAP算法的MATLAB浮點與FPGA定點的性能比較仿真結果可知,采用F(9,3)的定點量化標準,FPGA定點實現譯碼性能和理論的浮點仿真性能基本相近,并具有較好的譯碼性能。

綜上所述,在短幀情況下,MAX-LOG-MAP算法具有較好的譯碼性能,相對于MAP,LOG-MAP算法具有最低的硬件實現復雜度,并且Turbo碼譯碼延時也較小。所以,在特定的短幀通信系統中,如果采用Turbo碼作為信道編碼方案,MAX-LOG-MAP譯碼算法是硬件實現的最佳選擇。

評論