USB IP核的設計及FPGA驗證

整個解包過程如下:首先判斷接收的包是什么包,若為TOKEN包(0UT或IN或SOF或SETUP或ACK或NAK或STALL或PRE)則轉入到TOKEN包的處理進程,若為數據包(DATA0或DATAl)則轉入到DATA包的處理進程。在TOKEN包或DATA包中若發現數據有錯則丟棄此包并報錯。

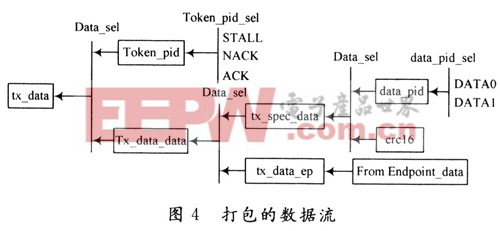

3.3.2 打包模塊

根據PE送來的PID組織相應的信息包,把要發送的數據安排在相應的數據包,或者組織令牌包。發送令牌包時,不必產生CRC5校驗位。在發送數據包時,需要把有效數據的CRCl6校驗位放在末尾一起發送。這個模塊主要就是如何把協議層引擎模塊送過來的數據進行打包,打包的概念其實質就是把要發送的數據根據其相應的信息安排相應的發送順序。同樣打包的過程中也不用考慮同步字段,同步字段在串口接口引擎層加入。整個打包數據流如圖4所示。

3.3.3 協議層引擎模塊

在USB設備中,某一個時刻和主機通信的只能是一個端點,當前操作都基于這個端點地址。主機不能同時和幾個端點進行通信,端點的屬性在設備和主機剛開始連接時進行的枚舉過程中已經確定,保存在各端點對應的寄存器中,比如是IN還是OUT端點,是支持控制傳輸、批量傳輸還是中斷傳輸的端點等。協議引擎模塊是整個協議層的核心控制單元,控制了其他所有模塊的工作方式,根據當前端點的配置或當前狀態處理傳輸事務,并在傳輸事務中實時更新控制與狀態寄存器。他的功能包括:有效處理IN,OUT和SETUP事務,確定當前傳輸事務要操作的端點地址,正確應答各種包和管理數據的發送和接收,同時實現USB協議中的錯誤恢復機制。

3.4 端點控制模塊和端點模塊

端點模塊:端點其實就是USB進行通信時,用于存數據的緩沖區,為了提高數據存取的速度,本IP核的端點設計成FIFO。端點控制模塊:主要是端點控制寄存器和端點狀態寄存器,此模塊中包含了USB IP核的頂層控制和狀態寄存器。如USB設備的狀態控制寄存器、設備地址寄存器、中斷屏蔽寄存器和中斷源寄存器等。為了增加靈活性,在設計時針對每一個端點分別設計了設置和功能相同但地址不同的寄存器,包括端點的控制狀態寄存器、中斷源寄存器、中斷屏蔽寄存器、緩沖區的指針寄存器。端點根據協議可以配置1到16個,在實際設計中根據本身系統需要可以對USB IP核配置端點數,增加了USB IP核端點可擴展性。

3.5 總線適配器模塊

此模塊是為了提高本IP核的可重用性而設計的。他主要包括WishBone總線接口、AMBA ASB總線接口和相應的配置寄存器。若使用于WishBone總線結構的SoC中,則在綜合前通過宏定義進行設置啟用WishBone總線接口,這樣整個USB IP核可以無縫接入WishBone總線結構的SoC中。若使用于AMBA ASB總線結構的SoC中,則在綜合前通過宏定義進行設置啟用AMBA總線接口無縫接入其SoC中。由于是在綜合前通過宏定義的,因此在實際綜合的時候,只會將宏定義的總線模塊綜合成實際電路,而不會兩個總線接口模塊都給綜合,節省資源。同時當此IP核要應用于其他的總線結構SoC中,如Altera的Avalon總線,則只要根據此總線協議再設計一個總線接口模塊,在綜合時啟用此總線接口模塊就可以將此IP核直接應用于此SoC中。因此本USB IP核對于不同總線的SoC利用總線適配器使具體較強靈活性,可重用性強。

評論