基于S3C2440嵌入式系統主板的電磁兼容性設計

2 嵌入式系統主板電磁兼容性設計

2.1 嵌入式系統主板

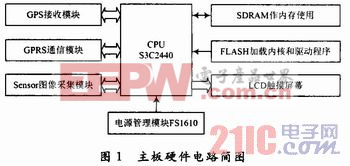

2.1.1 主板框圖

該設計研究的嵌入式系統是基于Samgsung S3C2440處理器的10層主板,系統主頻高達400 MHz,硬件配置有2顆64 MB的SDRAM,128 MB NAND FLASH,與CPU通信時,數據傳輸頻率高達133 MHz,同時還配置有LCD觸摸屏、Sensor圖像采集模塊、GPS模塊、GPRS無線通信模塊,以滿足系統功能上的需求,主板框圖如圖1所示。

2.1.2 主板存在的電磁干擾

在系統中,S3C2440的片內工作頻率FCLK可高達400 MHz,因此在PCB設計過程中,應該遵循高頻電路設計的基本原則。首先應注意電源的抗干擾設計,其次要注意信號線的布線技術,尤其是關注時鐘信號線、數據線和地址線。

2.2 電源的抗干擾設計

電源在向系統提供能源的同時,也將其噪聲加到所供電的電源上。電路中微控制器的復位線、中斷線,以及其他一些控制線最容易受外界噪聲的干擾。電網上的強干擾通過電源進入電路,不僅電池供電系統有高頻噪聲,電池本身也有高頻噪聲,而且模擬電路中的模擬信號更經受不住來自電源的干擾。

嵌入式芯片S3C2440的內核所需的直流電源電壓為1.3 V,I/O模塊及SDRAM的電源電壓為3.3 V。在電路設計時,一定要考慮電源的抗干擾技術。一般應在電源進入PCB的位置和靠近各器件的電源引腳處加上幾十微法到幾百微法的電容器,以濾除電源噪聲。還要注意在器件的電源與地之間加上0.1μF左右的電容器,以使能夠有效地抑制在電源線上傳導的高頻干擾,克服干擾信號對系統工作的影響。

2.3 共模差模EMI產生機理

2.3.1 共模EMI產生機理

共模干擾通常指兩根信號線上產生的幅度相等、相位相同的噪聲。共模干擾的特點是干擾的大小和方向一致,存在于電源任何一相對大地或中線對大地間。共模干擾也稱為縱模干擾、不對稱干擾或接地干擾輻射。是載流體與大地之間的干擾。

共模計算公式為:

式中:Ic表示電流強度;f表示共模電流的頻率;L表示電纜線長度;d表示測量天線到電纜的距離。

共模輻射是EMI中最主要的一種輻射干擾,通俗地說,是由于電路板地的“不平整”導致,或者連接線連接兩處的電位的高低差而導致連接線變成了輻射天線。然而電路板常常是由于地阻抗而引起電位的高低不平,從而能量由高到底有了輻射出來的條件。所以在電路設計與PCB排版時要特別注意PCB的地阻抗問題,從而更多地減小其產生的干擾。

2.3.2 差模EMI產生機理

差模干擾是幅度相等、相位相反的噪聲。差模干擾的特點是大小相等、方向相反,存在于電源相線與中線及相線與相線之間。差模干擾也稱為常模干擾、橫模干擾或對稱干擾,是施加于載流體之間的干擾。

差模輻射計算公式:

式中:ID表示電流強度;f表示共模電流的頻率;LS表示環路面積;d表示測量天線到電纜的距離。

2.4 共模差模EMI抑制措施

2.4.1 通常采用的抑制措施

通常減小共模輻射的方法有:

(1)減小地電位;

(2)使用去耦電容;

(3)使用鐵氧體磁環;

(4)使用共模電源濾波器。

通常減小差模輻射的方法有:

(1)減小環路面積;

(2)頻率越高,輻射越強,所以應盡量減小有用信號的高次諧波成分;

(3)采取屏蔽方法。

2.4.2 本文采用的源端端接抑制措施

所謂源端端接就是在傳輸線驅動端串聯端接一個等于特征阻抗的阻抗。

由共模輻射計算公式可以看到,要減小共模輻射,減小Ic和f是不可能的,d又是恒定值,只有減小L。由差模輻射計算公式,可以看出要想減小差模輻射,就是要減小LS即電流環路面積,多層板中信號走線的電流環路面積就等于介質的厚度乘以走線長度,在介質厚度恒定的前提下,減小差模輻射同樣歸結到減小信號走線L上。

然而縮短信號走線長度通常是不實用的,不過給傳輸線源端串聯端接一個等于特征阻抗的阻抗,就可以消除共、差模輻射的干擾。

源端串聯端接措施要求加一個電阻與輸出緩沖器串聯,緩沖器阻抗和端接電阻值的總和等于傳輸線的特性阻抗。此時,因為反射系數為O,任何由于在負載端存在的阻抗不連續所產生的反射干擾將在其達到源端時被消除,這樣可以減小噪聲、電磁干擾(EMI)及射頻干擾(RFI)。 linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論