基于DSP 的電壓閃變監測系統設計與實現

2 間接解調法誤差分析及修正

對采樣后計算得到的電壓均方根值序列Ui(n)進行頻譜分析時,由于FFT 存在頻譜泄露和柵欄效應,從而導致頻譜分析得到的閃變信號幅值產生較大的誤差,影響Pst的計算精度。調幅系數ΔUn = 10%,不同頻率fn的閃變信號經過FFT 運算后得到的計算值如表1 所示。可以看出,不同頻率的閃變信號經過FFT 運算后幅值都產生衰減,而且隨著頻率的增加衰減更加嚴重。

表1 調幅系數ΔUn = 10% 對應的計算值.

調幅系數ΔUn = 10% 對應的計算值

為了補償FFT 計算結果造成的幅值衰減,根據間接解調法提出衰減因子定義如下:

為了得到各個頻率的衰減因子,重復計算30 個波形,每次僅計算一個頻率成分,分別為: fn = 1,2,…,30 Hz,ΔUn = 10%;為了補償FFT 運算造成的幅值衰減,定義修正因子如下:

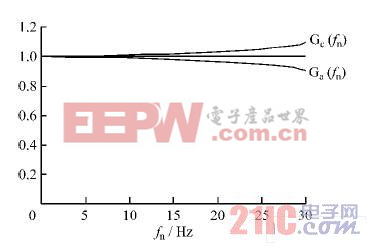

經過計算后,衰減因子和修正因子的曲線圖如圖1 所示。

衰減因子和修正因子曲線圖

圖1 衰減因子和修正因子曲線圖

修正后的幾個不同頻率的調幅系數如表2 所示。可以看出,修正后的調幅系數非常接近給定值,大大減少電壓閃變幅值的衰減。

表2 調幅系數ΔUn = 10%對應的計算值和修正值

調幅系數ΔUn = 10%對應的計算值和修正值

3 系統架構設計

3. 1 硬件架構設計

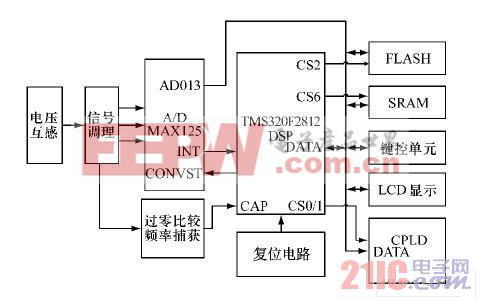

系統硬件設計是以TMS320F2812數字信號處理器為核心加上14 位雙極性高分辨率的A/D轉換器(MAX125) 和CPLD(EPM7128) 作為協處理器的基本架構組成。具體的硬件原理框架如圖2 所示。

經過信號放大、抗混疊濾波的電壓信號輸入到MAX125 進行模數轉換,根據采樣保持定理采樣頻率必須大于等于2 倍的信號頻率才能保證信號處理的完整性,因此,在A/D 轉換前要設置信號的采樣頻率。調理后的信號過零比較后,送DSP 進行頻率捕捉,將捕捉到的頻率用于初始化DSP 內部定時器。當定時時間到來時,進入定時器中斷子程序并打開A/D 采樣,轉換完成后MAX125 會產生一個硬件中斷告訴DSP 讀取數據。CPLD 作為協處理器,主要完成系統的組合邏輯、外設地址譯碼、數據輸入輸出緩沖鎖存、TTL /CMOS 電平信號兼容匹配等工作。

系統硬件架構框圖

圖2 系統硬件架構框圖.

該系統每半個工頻采樣128 點,然后送均方根模塊進行計算,得到一個電壓均方根值,在將所得的值暫存內部SRAM,連續采樣2. 56 s,得到一組256 Byte 的電壓均方根值,送到FFT 計算模塊進行FFT 變換,對變換后的結果進行修正,將修正后的結果保存在外部的Flash 中。

連續變換一段時間后( 如10 min),根據式(4)計算出電壓均方根值序列劃分Ui(n) 對應的瞬時閃變值Pi,然后再根據式(5) ~ (7)依次計算短時間閃變值Pst和長時間閃變值Ph。

評論