基于CPLD和嵌入式系統的高速數據采集系統的設計與實現

介紹一種基于CPLD和嵌入式系統的高速數據采集系統,并詳細闡述了系統的結構和軟硬件的實現方案。

關鍵詞:高速數據采集;CPLD;嵌入式系統

Design and Implementation of Highspeed Data Sampling System Ba sed on

CPLD and Embedded System

CPLD and Embedded System

LIN Dehui, DAO Kegang, DENG Yonggang, CHEN Sen

(Dept. of Information Engineering, China Institute of Metrology, Hang zhou 310018, China)

Key words: highspeed data sampling; CPLD; embedded system

1系統結構

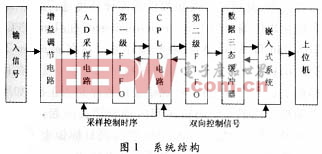

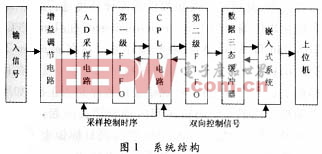

高速數據采集系統由高速ADC、CPLD、FIFO和嵌入式系統組成,系統結構如圖1所示。

高速數據采集系統由高速ADC、CPLD、FIFO和嵌入式系統組成,系統結構如圖1所示。

2.1嵌入式操作系統—Linux

Linux作為嵌入式操作系統有以下幾大優點:

(1)可應用于多種硬件平臺;(2)源代碼公開;(3)微內核直接提供網絡支持;(4)高度模塊化使添加部件非常簡單。

2.2硬件設計

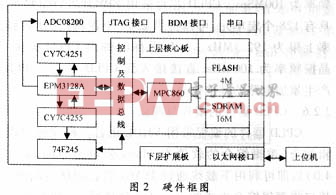

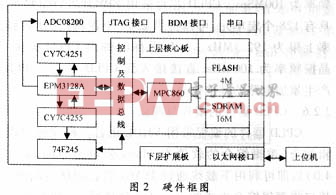

整個數據采集板采用雙層設計,上層是嵌入式系統的核心板,包括嵌入式系統CPU、FLASH和SDRAM等系統基本配置。MPC860的控制總線與數據總線通過核心板100線×3的接口插座與下面的擴展板各芯片通訊。硬件的結構框圖見圖2。

主站蜘蛛池模板:

陆川县|

鲁甸县|

江西省|

南华县|

青州市|

肥城市|

吉木萨尔县|

东至县|

日土县|

金门县|

随州市|

历史|

阿鲁科尔沁旗|

紫金县|

泰宁县|

浦江县|

万年县|

云和县|

循化|

阜阳市|

右玉县|

桦川县|

和田市|

宜良县|

雷波县|

靖江市|

周至县|

太湖县|

通渭县|

漳平市|

长武县|

多伦县|

惠来县|

贵德县|

旌德县|

宣恩县|

华宁县|

苍溪县|

大埔区|

湟中县|

福贡县|

Linux作為嵌入式操作系統有以下幾大優點:

(1)可應用于多種硬件平臺;(2)源代碼公開;(3)微內核直接提供網絡支持;(4)高度模塊化使添加部件非常簡單。

2.2硬件設計

整個數據采集板采用雙層設計,上層是嵌入式系統的核心板,包括嵌入式系統CPU、FLASH和SDRAM等系統基本配置。MPC860的控制總線與數據總線通過核心板100線×3的接口插座與下面的擴展板各芯片通訊。硬件的結構框圖見圖2。

嵌入式系統的CPU選用Motorola的MPC860芯片。它內部集成了微處理器和一些控制領域的常用外圍組件,特別適用于互聯網絡和數據通信。MPC860 PowerQUICC通信處理器可以根據用戶的不同要求提供2~4個串行通信控制器、數據緩存,各種級別的網絡協議支持。該處理器專為寬帶接入設備如路由器、集線器、交換機和網關等設計。

2.2.2系統內存

系統內存由3部分組成,MPC860內部集成了4KB數據Cache,以及片外擴展的Flash和SDRAM。Flash為2片Am29LV160D,總容量為4MB×8bit,用來存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,總容量為16MB×8bit。

2.2.3通用外設

MPC860的4個串行通信控制器(SCC)支持以太網、HDLC/SDLC、HDLC總線(用以實現基于HDLC的局域網)、AppleTalk、UART、比特流透明傳輸、基于幀的透明傳輸(CRC可選)、支持PPP(Point to Point Protocol)的異步HDLC等標準協議,只需很少的外圍芯片就可以實現串行口和USB Slave接口。MPC860外擴一片LXT905PC就方便地實現了一個10BASET的以太網接口。

2.2.4嵌入式系統調試

MPC860處理器支持BDM(背景調試模式),完成板卡硬件檢測、下載、運行、燒寫FLASH、內核調試、單步調試等最底層的調測功能。在背景調試模式下,通過向CPU發送命令,可以實現對寄存器、系統存儲器的訪問。

另外,在調試時還可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC編譯環境在windows下進行應用程序的開發和調試。

2.2.5A/D轉換和CPLD電路

A/D采樣采用的器件為ADC08200,精度為8位,采樣頻率由20MSps至200MSps,本電路中的A/D采樣頻率為100MSps。CPLD芯片采用EPM3128ATC144-5,具有128個宏單元,可以提供2500個邏輯門,計數頻率上限為192.3MHz。A/D采樣時鐘由CPLD提供。晶振頻率為100MHz,直接接入到CPLD中,由CPLD產生累加電路的其他信號。

2.2.6CPLD器件的編程與調試

CPLD器件的編程采用VHDL語言。程序經過邏輯綜合(邏輯綜合的軟件為Altera公司的QuartusⅡ 4.0)后即可利用下載線通過JTAG(聯合測試行動組)接口將邏輯綜合生成的*.pof文件燒寫到CPLD器件中,然后即可測試芯片的功能。 linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

2.2.2系統內存

系統內存由3部分組成,MPC860內部集成了4KB數據Cache,以及片外擴展的Flash和SDRAM。Flash為2片Am29LV160D,總容量為4MB×8bit,用來存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,總容量為16MB×8bit。

2.2.3通用外設

MPC860的4個串行通信控制器(SCC)支持以太網、HDLC/SDLC、HDLC總線(用以實現基于HDLC的局域網)、AppleTalk、UART、比特流透明傳輸、基于幀的透明傳輸(CRC可選)、支持PPP(Point to Point Protocol)的異步HDLC等標準協議,只需很少的外圍芯片就可以實現串行口和USB Slave接口。MPC860外擴一片LXT905PC就方便地實現了一個10BASET的以太網接口。

2.2.4嵌入式系統調試

MPC860處理器支持BDM(背景調試模式),完成板卡硬件檢測、下載、運行、燒寫FLASH、內核調試、單步調試等最底層的調測功能。在背景調試模式下,通過向CPU發送命令,可以實現對寄存器、系統存儲器的訪問。

另外,在調試時還可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC編譯環境在windows下進行應用程序的開發和調試。

2.2.5A/D轉換和CPLD電路

A/D采樣采用的器件為ADC08200,精度為8位,采樣頻率由20MSps至200MSps,本電路中的A/D采樣頻率為100MSps。CPLD芯片采用EPM3128ATC144-5,具有128個宏單元,可以提供2500個邏輯門,計數頻率上限為192.3MHz。A/D采樣時鐘由CPLD提供。晶振頻率為100MHz,直接接入到CPLD中,由CPLD產生累加電路的其他信號。

2.2.6CPLD器件的編程與調試

CPLD器件的編程采用VHDL語言。程序經過邏輯綜合(邏輯綜合的軟件為Altera公司的QuartusⅡ 4.0)后即可利用下載線通過JTAG(聯合測試行動組)接口將邏輯綜合生成的*.pof文件燒寫到CPLD器件中,然后即可測試芯片的功能。 linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論