在嵌入式設計中降低CPLD的功耗

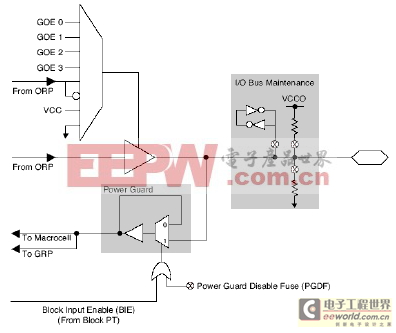

圖4:Power Guard電路。

根據實際的應用使用Lattice的Power Guard或其他方法來禁用時鐘至選定的CPLD的輸入引腳,這樣可以大大降低動態功耗。尤其是如果邏輯信號的時鐘頻率超過30兆赫時,這些方法特別有用。圖5說明了可以用選擇邏輯時鐘技術實現潛在的節省功耗的方法。

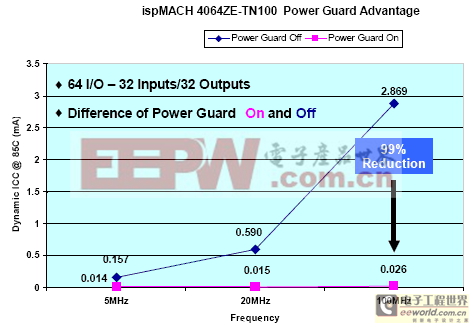

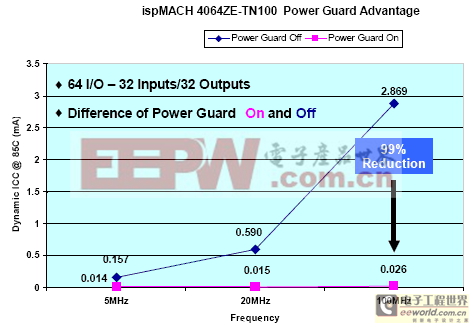

圖5:Power Guard 節省的功耗。

動態功耗管理

設計人員需要關注兩種類型的動態功耗。運行功耗預算的第一部分是CPLD需要實際工作時的那部分。管理策略的其他部分涉及關掉輸入至此刻不需要的CPLD的部分,阻止它們切換,或在可能的情況下將它們全部關閉。

精密的電源管理

雖然CPLD邏輯的許多部分很可能被連續使用,在有意義的時間段內不能禁用,因此使用低電源電壓仍然可以節省功耗。由于功耗是電壓平方的函數,用1%的精確開關穩壓器,可讓設計運行于CPLD工作范圍的下限,您可以節省相當多的功耗。例如,如果一個標稱值為1.8V的CPLD工作在1.65V,它大約少消耗30%的功耗,這還不包括在較低Vcc的情況下泄漏電流的減少。

選擇邏輯門

如同大多數的CPLD,ispMACH 4000ZE具有一個功能(萊迪思稱為“Power Guard” 功耗衛士),當它們不需要相關的邏輯時,可禁用單獨的輸入。主機處理器、其他的外部邏輯,或CPLD的其他部分可以使用器件的塊輸入使能線,以保持CPLD的邏輯選定的塊被時鐘控制(圖4)。例如,如果CPLD的某個部分被用作解碼器電路,只有該功能正在使用時,主處理器可以使它能工作,使之能夠在其余的時間保持休眠狀態。

圖4:Power Guard電路。

根據實際的應用使用Lattice的Power Guard或其他方法來禁用時鐘至選定的CPLD的輸入引腳,這樣可以大大降低動態功耗。尤其是如果邏輯信號的時鐘頻率超過30兆赫時,這些方法特別有用。圖5說明了可以用選擇邏輯時鐘技術實現潛在的節省功耗的方法。

圖5:Power Guard 節省的功耗。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論