在嵌入式設計中降低CPLD的功耗

從事便攜式或手持產品設計的工程師都明白對于如今的設計,最大限度地降低功耗是必不可少的要求。但是,只有經驗豐富的工程師理解盡可能地延長系統的電池壽命的那些微妙但又重要的細節。本文中我們將重點放在這些經驗豐富的專家是如何使用超低功耗的復雜可編程邏輯器件(CPLD),并從他們的嵌入式設計中的I/O子系統節省每個微瓦的方法。

本文引用地址:http://www.104case.com/article/151104.htm我們首先來了解在嵌入式設計中如何降低CPLD的功耗、電路板的面積和元器件成本。下一步,我們將看到在待機模式下如何盡量降低CPLD的功耗,不僅要仔細地選擇器件,而且還要選擇一個合適的總線駐留方案。器件工作期間,我們對節省功耗的探討將包括選擇邏輯門、智能I/O設計和精密的電源電壓管理技術。

嵌入式工程師青睞的器件CPLD

盡管在最先進的新興應用中它們特別受歡迎,CPLD的成本低,體積小和低功耗的特性使他們成為幾乎所有的手持式或便攜式設計的首選。在這些應用中,它們常用來整合邏輯功能,擴展主處理器的I/O功能和監控關鍵的輸入,從而使處理器有更多的時間處于低功耗睡眠模式。

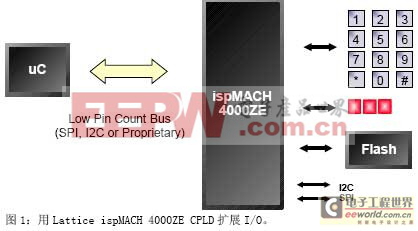

用作I/O的擴展器件時,像ispMACH 4000ZE這樣的CPLD器件(圖1)給予簡單的嵌入式處理器額外的信號線和處理功能,他們能夠支持顯示器、按鈕、發光二極管,串行或并行I/O,或存儲接口。設計人員還經常利用它們作為設計中通用處理器和更多的專業芯片組之間的緩沖,還能用于其他的應用,如智能手機、GPS系統,遠程工業傳感器和數碼攝像機。

圖1:用Lattice ispMACH 4000ZE CPLD擴展I/O。

待機功耗的基本知識

掌握CPLD功耗的第一步是了解器件在工作時的情況和待機(也稱為靜態)時的狀態。由于許多CPLD在大部分時間是處于待機狀態,我們首先會仔細考察這個經常被誤解的模式。

加電壓至器件輸入部分,但其內部邏輯還沒有被時鐘控制,此時CPLD是處于待機狀態。在此狀態下,因為它的泄漏和偏置電流(雖然大大低于實際的操作),CPLD仍然有一些功耗。泄漏電流隨溫度、工作電壓和制造工藝而變化。

負載產生了可編程邏輯器件內的偏置電流,如內部振蕩器、I/O的上拉/下拉電路和其他固定開銷,而不管器件的邏輯功能是否正在使用。與泄漏電流不一樣,在一定的溫度和電壓范圍內偏置電流是相對穩定的,它們可以用合適的內部配置所控制。 Script type=text/javascript>function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w m){return;} else{ var h = $(Id).height; $(Id).height = parseInt(h*m/w); $(Id).width = m; } } window.onload = function() { var Imgs = $(content).getElementsByTagName(img); var i=0; for(;i

用明智的方法管理泄漏電流

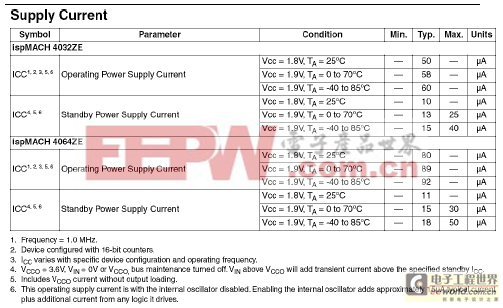

由于可編程邏輯器件的泄漏電流主要取決于它是怎樣制造的,第一步就是要密切關注候選器件制造商提供的數據手冊的規范。只是簡單地購買廣告所述的低功耗器件并不能保證如你期望設計中達到的指標完全一樣。經驗豐富的設計師明白尋找“典型”和“最大”電流之間的實際關系需要根據具體的應用(圖2)做出解釋。在許多應用中,數據手冊中列出的所謂典型電流中提供了一個非常有用的CPLD汲取電流的近似值。然而,有幾個問題需要加以探討,以確保對設計的估計和實際功耗保持相對接近。

圖2:供給電流規范。

首先需要考慮的事項是CPLD占整個系統功耗的比例。如果這是一小部分,比如說5%~10%,即使最壞的情況將引起整個功耗有相對較小的變化。如果CPLD需要20%或以上的功耗預算,也許是開始根據額定待機電流考慮偏置設計的時候了,額定待機電流接近數據手冊中列出的最大電流。您還應該考慮設計中CPLD(以及其他器件)的數量。由于電路板上元器件數量的增加,總功耗接近總的典型額定電流的概率也隨之增加。最后,如果您的產品以驅動它至最壞情況的功耗級別為目標,那么您需要考慮潛在影響:較高的功耗會縮短產品的壽命嗎?它是否會成為火災的隱患?

如果您仔細察看圖2中的數據,你可能注意到,待機功耗還根據工作溫度和Vcc(電源電壓)而變化。這是因為CPLD的漏電流會隨溫度升高而增加。事實上,使您的設計完美將改善其待機功耗。由于漏電流與Vcc密切相關,保持電源電壓盡可能的低可以節省更多的功耗。由于仔細的電源電壓管理能夠節省更多的動態功耗,在涉及運作功耗管理時,我們會對這個方面進行探討。

設置偏置電流

通過選擇合適的器件可以控制CPLD的泄漏電流,現在到了運用你的工程技能調整偏置電流的時候了。用來管理偏置電流的技術大致分為兩種類型:

確保CPLD的待機配置不與上拉/下拉或相關的其他器件所用的總線駐留技術相沖突;動態控制內部功能塊(如振蕩器),使他們只開啟所需要的部分。具體取決于所使用的CPLD,這是增加更多的待機時間到設計中的好方法。

并行駐留101方案

在許多設計中,嵌入式主處理器可以使用自己的總線駐留方案,以保持在總線或I/O上所需的邏輯電平,所以你只須為CPLD的待機模式做準備,確保其激活總線的管理功能被禁用。在其他應用中,總線上其他地方的上拉或下拉電路也可以緩解在待機期間CPLD必須管理總線的情況。

但是,不需要CPLD做任何事情并不意味著你也不需要做任何事情。花些時間驗證只有一個設備驅動總線是一個重要的任務,因為單個引腳上的邏輯沖突可導致待機功耗為整個芯片標稱值10uA 閑置功耗的2~15倍。

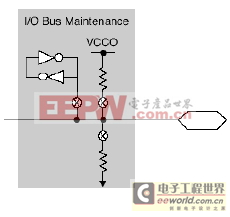

在主總線駐留機制無法使用情況下,可以使用上拉/下拉,以及在大多數現代的CPLD中擁有的總線保持功能。如同大多數同類器件,萊迪思的ispMACH 4000ZE CPLD的I/O引腳都配備了可選的上拉和下拉電阻,在待機狀態(圖3)可提供合適的邏輯電平。4000ZE系列還配備了節省功耗的總線保持功能(也稱為總線保持):一種弱激活驅動電路可設置為激活或零,同時產生比簡單的電阻器消耗小得多的功耗。一點忠告:雖然總線保持功能可大大節省功耗,但必須肯定它是唯一的在線有源器件,否則會有吸入大電流的風險。

圖3:CPLD的總線管理選擇。

動態功耗管理

設計人員需要關注兩種類型的動態功耗。運行功耗預算的第一部分是CPLD需要實際工作時的那部分。管理策略的其他部分涉及關掉輸入至此刻不需要的CPLD的部分,阻止它們切換,或在可能的情況下將它們全部關閉。

精密的電源管理

雖然CPLD邏輯的許多部分很可能被連續使用,在有意義的時間段內不能禁用,因此使用低電源電壓仍然可以節省功耗。由于功耗是電壓平方的函數,用1%的精確開關穩壓器,可讓設計運行于CPLD工作范圍的下限,您可以節省相當多的功耗。例如,如果一個標稱值為1.8V的CPLD工作在1.65V,它大約少消耗30%的功耗,這還不包括在較低Vcc的情況下泄漏電流的減少。

選擇邏輯門

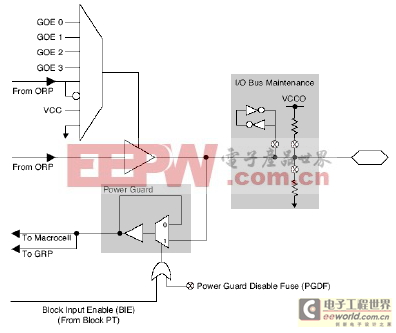

如同大多數的CPLD,ispMACH 4000ZE具有一個功能(萊迪思稱為“Power Guard” 功耗衛士),當它們不需要相關的邏輯時,可禁用單獨的輸入。主機處理器、其他的外部邏輯,或CPLD的其他部分可以使用器件的塊輸入使能線,以保持CPLD的邏輯選定的塊被時鐘控制(圖4)。例如,如果CPLD的某個部分被用作解碼器電路,只有該功能正在使用時,主處理器可以使它能工作,使之能夠在其余的時間保持休眠狀態。

評論