基于FPGA的視頻傳輸流發送系統設計方案

系統以字節同步的方式接收MPEG-2傳送包,接收的參考時鐘是采用固定的27MHz的時鐘頻率。接著,對字節進行8B/10B編碼,對出現的每一個8bit字節產生一個10bit的字,使這些10bit字通過以固定輸出比特率270Mbps工作的并/串轉換。

將8B/10B編碼劃分為3個模塊實現,較好地反映了8B/10B編碼的特點,實現流程清楚,容易編寫代碼。具體實現步驟為: ① 判斷是特殊字符還是數據; ② 若是特殊字符(3B4B),根據RD極性直接取值; ③ 若是數據,根據RD極性和前一個10bit模塊的編碼情況確定當前6 bit的取值; ④ 根據當前6 bit編碼值確定當前4 bit的編碼取值。⑤ 將當前6 bit編碼和當前4bit編碼組成當前10bit編碼輸出。

3.4 并串轉換模塊

在完成8B10B編碼以后,將信號送至并串轉換模塊轉換為串行數據流,通過270MHz時鐘將串行信號送出,ASI接口采用兩線差分方式進行串行數據傳輸。

4 測試結果

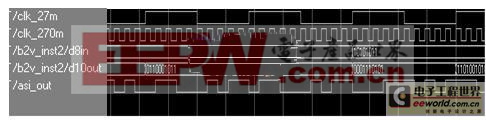

首先對ASI發送系統進行功能仿真,仿真平臺為ModelSim6.0,本設計中,ASI發送系統的輸入輸出的仿真波形如下圖所示:

圖 2 ASI發送系統的仿真波形

仿真結果表明,輸入信號與編碼信號之間順序相差一個碼元周期,輸出抖動被完全消除。

本文中的ASI接口測試由Honeywell公司的攝像頭、自行研制的MPEG2編碼板(視頻壓縮芯片為MB86391)、MPEG2解碼器、顯示器構成,如圖3所示。

圖 3 系統組成

ASI發送測試為:Honeywell公司的攝像頭和自行研制的MPEG2編碼板輸出符合MPEG2標準的TS流,通過標準SPI口送給本文的ASI轉換系統的SPI輸入,而經SPI到ASI的轉換,通過BNC接頭的有線電纜送給解碼器的ASI口輸入,解碼后的視頻輸出送給顯示器,連續播放數十小時,圖像清晰且顯示正常無誤。

實驗結果證明,采用本文方法設計的ASI發送系統,符合標準ASI接口規范,能有效可靠的實現SPI-ASI的編碼功能和高速串行數據流的發送功能。

5 結語

本文作者創新點: 在分析ASI發送系統機理的基礎之上,提出一種使用FPGA完成ASI發送系統的實現方案,并使用VHDL語言在Altara的FPGA上實現了硬件電路,仿真結果和實際測試完全正確。該方案層次分明、結構簡潔、編碼速度快、輸出抖動小,與現有的使用專用芯片CY7B923的方法相比,具有更大的靈活性,為高速ASI數傳的應用前端提供了條件。

評論