基于TMS320DM6437的McBSP與EDMA實現串口通信

一個參數RAM的長度為32個字節。首先是32 bit的可選參數OPT,對于可選參數,通過對各個位置0或1設置事件優先級,數據單元大小,源地址/目的地址變更模式,傳輸結束代碼,是否使能傳輸參數鏈接(LINK)功能,同步傳輸方式等。SRC和DST為EDMA傳輸所需的源地址和目

的地址。SRCBIDX和DSTBIDX用于二維傳輸中,表示一個ARRAY的開始到下個ARRAY的開始所跨越的字節數。SRCCIDX和DSTCIDX用于三維傳輸中,一個FRAME的開始到下個FRAME的開始所跨越的字節數。BCNTRLD:三維傳輸里需要重新加載的BCNT。LINK:傳輸完成后重新加載的參數RAM地址,默認是LINK到空參數RAM。

在此實例中采用的雙緩沖結構,即在DSP緩沖區內開辟2塊緩沖用于并行處理FPGA通過McBSP傳過來的數據。當EDMA往PingBuffer里傳輸數據時,CPU即可處理PongBuffer里的數據,當工作完成后,彼此又交換緩沖區,EDMA往PongBuffer里寫數據,CPU處理PingBuffer里的數據。為了實現雙緩沖結構,采用了EDMA提供的LINK功能,即將不同的EDMA傳輸參數RAM鏈接起來,組成一個傳輸鏈,在傳輸鏈中,一個傳輸的結束會導致自動從參數RAM中裝載下一個傳輸需要的事件參數。在具體程序中,只需將Ping通道的參數RAM LINK到Pong通道,同時將Pong通道的參數RAMLINK到Ping通道即可。

2.2.2 EDMA接收數據配置實現

開發環境采用CCS 3.3。通過調用LLD API實現對EDMA Driver的配置以及傳輸操作。

在使用EDMA3 Driver之前必須首先對其進行初始化。EDMA3 LLD提供了2個API進行相關工作。EDMA3_DRV_create和EDMA3_DBV_open。前者用于創建一個EDMA3 Driver對象,后者用于開啟對應的EDMA3 Driver通道。

創建并開啟EDMA3 Driver通道后,即可為此通道分配資源以及初始化其配置。首先調用EDMA3_DRV_requestChannel請求分配一個DMA通道,隨后對該通道的參數RAM進行配置,以滿足傳輸需要。EDMA3_DRV_setSrcParams用于設置該EDMA通道接收數據源地址為McBSPO的DRR寄存器,地址為0x01D00000,地址計數模式為遞增模式。EDMA3_DRV_setDestParams設置該EDMA通道接收數據目的地址為DSP片內存儲區PingBuf-fer首地址,確保第一次傳輸數據是到PingBuffer,地址計數模式同樣為遞增模式。EDMA3_DRV_setSrcIndex用于配置源地址計數索引值,由于源地址為McBSPO的DRR寄存器,固定不變,所以srcBidx=0,srcCidx=0。接著調用EDMA3_DRV_setDestIndex配置目的地址計數索引值,由于接收數據為32 bits,所以sreBidx=srcCidx=4,這是因為DSP內的最小計數單元為一個字節,8bit。EDMA3_DRV_setTransferPamms配置剩余的參數RAM傳輸參數,包括設置ACNT=4,BCNT=2 048,CCNT=1,采用一維傳輸A-SYNC。

接下來是Ping/Pong傳輸的程序實現。需再調用EDMA3_DRV_requestChannel兩次,替Ping/Pong各自分配一個通道,于是,一共有3個通道,對應3個參數RAM。Ping通道的參數RAM與主通道的參數RAM完全一致,Pong通道的參數RAM與主通道相比,只需將Pong通道接收數據目的地址改為PongBuffer首地址。隨后調用EDMA3_DRV_linkChannel 3次,分別將主通道和Ping通道LINK,Ping通道和Pong通道相互LINK。

2.2.3 EDMA中斷實現

結合DSP/BIOS設置了EDMA中斷,以便在一個接收Buffer被填滿時,產生的EDMA中斷可通知DSP處理該Buffer的數據。

TMS320DM6437中,EDMA的128個通道只產生一種中斷,當一個通道傳輸完成后,IPR(Interrupt Pending Register)寄存器里的相應位會被置1,EDMA中斷處理器通過查詢IPR寄存器確定是哪個通道完成了傳輸,并調用相應的中斷服務程序。

EDMA LLD中中斷的設置通過調用EDMA3_DRV_requestChannel實現。該函數的參數中跟中斷有關的為eventQ(與通道優先級相關),tceCb(回調函數,即通道傳輸完成后所調用的中斷服務程序)。本例中,設置eventQ=0,保證最高優先級,tceCb=edma_isr,該函數的作用是在通道傳輸完成后發送一個旗語信號給信號處理程序,通知其對收到的數據進行處理。此外,還需調用EDMA3_DRV_setOptField將參數RAMOPT參數中TCINTEN位置1,以使能EDMA中斷。隨后,利用DSP/BIOS將EDMA中斷源和DSP的可屏蔽中斷5連接起來,具體參數在DSP/BIOS配置文件中的HWI模塊設置,如圖3所示。本文引用地址:http://www.104case.com/article/150982.htm

最后,由于選用了TMS320DM6437的可屏蔽中斷5,還需使能IER寄存器里的對應位,C64_enableIER(C64_EINT5)。

2.2.4 EDMA發送數據配置實現

EDMA發送數據程序流程和接收數據程序流程大略一致,但較為簡單。只需請求一個EDMA傳輸通道,配置其源地址為DSP內部存放FPGA所需數據內存首地址,目的地址為McBSP的DXR寄存器。其余參數和EDMA接收數據通道參數相同。

3 實現結果

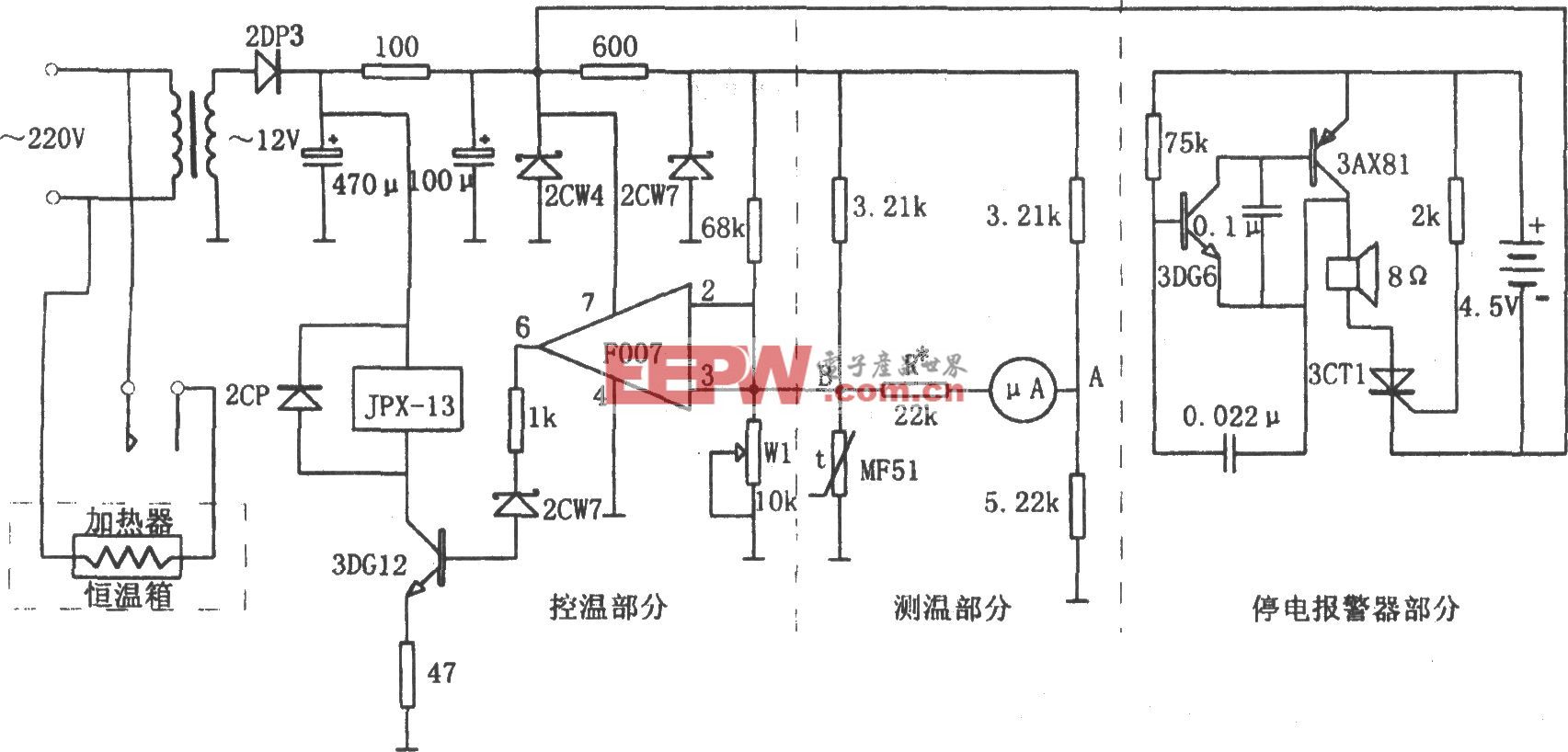

配置好MeBSP和EDMA后,啟動FPGA傳輸數據,DSP做好接收和發送數據的準備,實驗中,FPGA連續不斷地發送自加地數給DSP,而DSP只發送2048個32 bit的從0開始的自加數據給FPGA。實驗結果表明,DSP內部的PingBuffer區和PongBuffer區能連續不斷的收到FPGA傳輸過來的數

據。某一時刻的PingBuffer區和PongBuffer區內部數據如圖4所示,能看出實驗實現了上述功能。

評論