TMS320C672x系列浮點DSP的EMIF研究與應用

EMIF控制SDRAM工作時,當行地址選通引腳EM_RAS有效時,SDRAM通過A0~A11獲取行地址;當列選通引腳EM_CAS有效時,SDRAM通過A0~A11獲取列地址。EMIF訪問的外部SDRAM空間地址映射為0x80000000-0x8FFFFFFF,由表1的地址映射知,如果要存儲16位的short int型數據到SDRAM,每次邏輯地址需要加2,如:*(short int*)(0x80000000+i*2)=short int i;存儲32位的int型數據每次地址需要加4,如:*(int*)(0x80000000+i*4)=int i。

3 EMIF與Flash的設計

當DSP脫機運行時,系統上電或復位后,DSP系統自帶的Bootloader將一段存儲在外部的非易失性存儲器中的代碼搬移到內部高速存儲單元中執行。這樣既利用了外部存儲單元擴展DSP本身有限的ROM資源,又充分發揮了DSP內部資源的效能。TMS320C672x系列DSP只支持一種硬啟動選項,即從內部ROM地址0x00000000啟動,其他啟動選項由存儲于ROM的軟啟動器實現。軟啟動器使用CFGPIN0和CFGPIN1寄存器,這2個寄存器在復位時捕捉相關器件引腳的狀態,以決定進入那種啟動模式。ROM主要有4種自啟動模式:從EM_CS2空間的并行Flash啟動、利用SPI0或I2C1主模式從EEPROM啟動、利用SPI0或I2C1從模式從外部MCU啟動以及利用UHPI口從外部MCU啟動。這里分析了從EM_CS2空間的并行Flash啟動模式,給出了高密度、非易失性的電可擦除存儲器AM29LV800BB-90EC(512 Kx16 Bit)與EMIF的接口設計方案。

3.1 Flash的硬件連接

AM29LV800BB~90EC型Flash具有19根地址線,而TMS320C6722 EMIF只有14根地址線(EBA0~EBA1、EA0~EA11)。因此,EMIF與Flash連接時地址線不夠用,需要擴展高位地址線,這里提出兩種擴展方法:GPIO擴展和CPLD地址鎖存器擴展。

3.1.1 GPIO擴展

TMS320C672X MCASP通道的各功能引腳都可以作為通用的I/O接口,直接與Flash存儲器的高位地址線連接。硬件原理圖如圖5所示研。圖5中,任何在復位時可下拉的GPIO引腳都可用于控制Flash啟動器的地址線A[18:13]。

3.1.2 CPLD地址鎖存器擴展

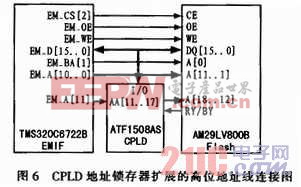

在CPID中設計一個地址鎖存器74L273,通過74L273的輸出口擴展7根高位地址線A11~A17,分別與Flash的A12~A18連接。EMW的EM_A[11]作為CPLD鎖存器的輸入選通端選,EMIT數據線作為鎖存器的輸入,如圖6所示。

3.2 FLash的軟件配置

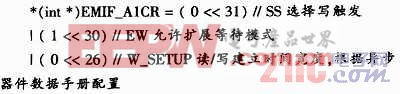

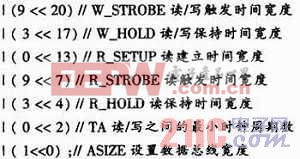

在EMIF異步接口中,AICR是唯一需要編程的寄存器。根據Flash器件的特性,配置如下:

3.3 Flash的軟件操作

TMS320C672x DSP的存儲器中EMIF訪問的外部異步器件Flash空間地址映射為0x90000000~0x9FFFFFFF之間。由于Flash數據總線寬度為16位,因此在硬件設計時選用半字尋址,即EMIF的BA[1]連接Flash的A[0]。根據配置寄存器A1CR中數據總線寬度的配置,訪問異步器件時TMS320C6722中內部地址和EMIF地址引腳對應如表1所示。

存儲器相關文章:存儲器原理

評論