一款基于S3C2440A的銀行評價器的設計

以上都是針對微處理器S3C2440A要做的一些軟件開發,但嵌入式系統是一個實時操作性很強的東西,尤其是在某些具體產品設計上,容易出現一些問題。而這些問題的根源,往往出現在時序問題上。基于這樣的考慮,嵌入式系統往往就要引入CPLD來協調微處理器與其他外圍電路或設備的時序問題。

3.2 XL95144XL的軟件開發

XL95144XL是一款使用非常廣泛的CPLD。CPLD的編程語言主要有兩種:VHDL和Verilog HDL語言。在這里,采用VHDL語言來實現對XL9514 4XL編程。VHDL語言是一種描述、模擬、綜合、優化和布線的標準硬件描述語言,具有很強的移植能力,它可以從一個模擬器移植到另一個模擬器上、從一個綜合器移植到另一個綜合器上或者從一個工作平臺移植到另一個工作平臺上去執行。

在這個銀行評價器軟件中,CPLD實現的功能主要有兩個:一個是外圍設備的地址分配功能,實現外圍設備與S3C2440A之間的正確地址連接;第二個就是協調時序或同步信號,使得相關的外圍設備能夠正常工作。XL95144XL實現這兩個功能非常容易方便,程序量雖然不大,但起到的作用很大。

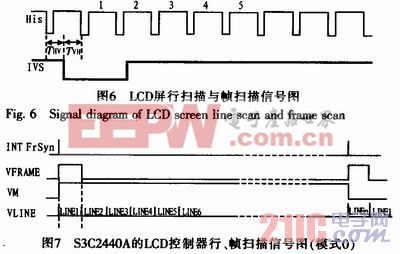

例如,選用一款TFT型LCD液晶屏進行圖像顯示,該款屏對于行掃描信號與幀掃描的時序要求很嚴格,如圖6所示。如果出現一定時序偏差的話,就容易出現局部“花屏”現象,而微處理器S3C2440A工作后給出的掃描信號的時序并不十分滿足液晶屏的指標參數,如圖7所示。所以,就需要把掃描信號通過CPLD編程進行協調控制。本文引用地址:http://www.104case.com/article/150951.htm

從圖6、圖7可以看出,掃描信號時序不能保證一致性,勢必會帶來產品設計上的一些缺陷,有的問題甚至會很直觀地反映出來,這也就是在嵌入式系統中要加上CPLD的一個重要原因之一了。

3.3 下載和調試

軟件編寫完成后,就要實現下載。ARM和CPLD都有各自的JTAG下載端口,通過不同的下載線與PC機的通信口進行連接,然后在PC機上使用超級終端分別下載相應的軟件包到目標板上運行調試。

4 結論

本文中的銀行評價器是基于嵌入式系統開發設計的,它相比于以往的數碼管采用數字顯示模式的評價器而言,視覺效果有了一個質的飛躍;再者,它也取消了數字按鍵式的評價方式,采用了觸摸屏進行客服評價,起到了更好的效果。與此同時,在不需要進行客服操作的時候,還可以運行其他的一些輔助軟件,在一定程度上起到了一個宣傳機的作用。由此可見,這樣一款基于ARM所設計的銀行評價器,功能強大

且易擴展,性能也更好,而且隨著電子產業的發展,嵌入式系統的應用越來越廣,采用ARM開發設計的評價器來代替傳統的數碼管式評價器也成為了必然的趨勢。

評論