基于嵌入式的電纜故障檢測儀設計

3 硬件設計

以Altera公司的Cyelone II系列FPGA器件EP2C20為核心,利用其Nios軟核功能設計了微處理器,并完成了相關電路的設計。通過編程FPGA器件定制脈沖發生、高速時鐘以及高速數據存儲FIFO等模塊,以此為基礎設計了脈沖發送和接收電路以及高速數據采集和處理電路。

3.1 微處理器系統

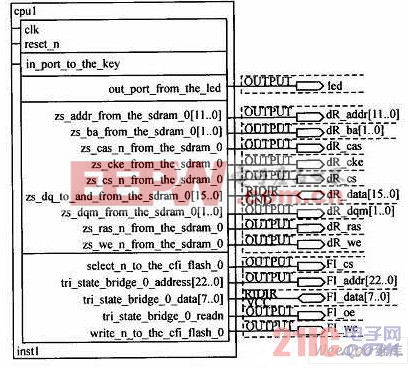

簡單來說,Nios是一種處理器的IP核,設計者可以將它放到FPGA中。Nios軟核處理器是一種基干流水線的精簡指令集通用微處理器,時鐘信號頻率最高可達75 MHz。采用Flash來存儲啟動代碼和應用程序,當系統復位或加電啟動時,Flash中的啟動代碼將被執行。采用SDRAM存儲應用程序的可執行代碼和數據,為程序提供運行空間。Nios軟核與Flash和SDRAM的連接在FPGA中的設計如圖2所示。

圖2 Nios軟核與Flash和SDRAM的連接在FPGA中的設計

3.2 探測脈沖的產生

故障檢測所用脈沖信號的寬度為20~100 ns,FPGA的工作時鐘可以達到200 MHz,在其中生成減法計數器可產生滿足脈寬要求的脈沖信號。減法計數器產生脈沖的幅度受限于FPGA的工作電平,對檢測來說是不夠的,因此從FPGA中出來的方波脈沖還要經過放大,才可以耦合到被檢測線纜中去。SN74LVC4245A用作電平轉換。sta和pulse_input均來自FPGA。本設計采用的是5 V脈沖幅度,脈沖的饋送采取了晶體管射極驅動的方式。這種驅動方式比較簡單,適用的器件也比較多。

3.3 A/D轉換電路

檢測脈沖的寬度為20~100 ns,相應的數據采樣率在20 MHz和100 MHz之間變化,一般的A/D芯片很難滿足采樣的要求,而用多片A/D芯片在成本和設計上都比較困難。這里選用美國NS公司的ADC08100,其采樣速率為20~100 Msps,此時采樣的功耗為1.3 mW/Msps,采樣的功耗會隨著采樣時鐘增加而增加,但是采樣的特性不會受到影響,因此在采樣率多樣的系統中一個芯片可以起到多個芯片的作用。根據采樣速率的不同,通過一個時鐘控制模塊產生相應的采樣時鐘信號,使芯片工作在所要求的速率之下,既可以節約成本,又可以簡化設計。ADC08 100和FPGA配合使用,可以方便地改變采樣時鐘,具有很大的靈活性。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論