基于DSP TMS 3 2 0F2 8 1 2的智能接口板設(shè)計(jì)

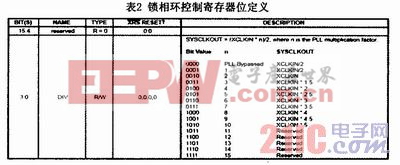

該接口板采用30M石英晶體提供時(shí)鐘,XPLLDIS引腳上拉使能PII模塊,倍頻選擇最大的XCLKIN×5=150MHz。

1.2.2 復(fù)位電路

復(fù)位電路會(huì)中斷F2812的執(zhí)行,復(fù)位板上資源,同時(shí)使處理器從0x3FF000地址開始執(zhí)行指令序列。F2812的復(fù)位可由外部復(fù)位管腳引起。

F2812外部復(fù)位源采用MAX706芯片進(jìn)行復(fù)位,MAX706復(fù)位的產(chǎn)生條件有以下3種情況:

(1)上電復(fù)位,當(dāng)Vcc>4.40V(典型值)時(shí)產(chǎn)生復(fù)位,并保持200ms復(fù)位有效;

(2)掉電復(fù)位,當(dāng)Vcc4.40V(典型值)時(shí)產(chǎn)生復(fù)位,此時(shí)可防止對(duì)存儲(chǔ)器進(jìn)行錯(cuò)誤寫入;

(3)手動(dòng)復(fù)位,當(dāng)手動(dòng)復(fù)位信號(hào)有效,產(chǎn)生復(fù)位,用于調(diào)試。

MAX706的復(fù)位信號(hào)形成F2812的上電復(fù)位輸入,使系統(tǒng)所有資源復(fù)位。復(fù)位電路如圖7所示。

1.3 串行總線處理電路

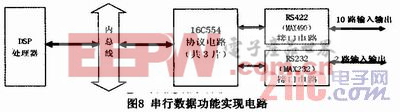

本模塊串行數(shù)據(jù)的接收和發(fā)送都采用TL16C554協(xié)議芯片來完成,RS422和RS232總線傳輸通過不同的接口芯片完成電平轉(zhuǎn)換,其功能框圖如圖8所示。

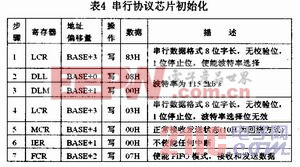

16C554通過對(duì)各個(gè)寄存器的編程完成串行數(shù)據(jù)的初始化及傳輸,在上電初始化時(shí),本模塊將串行數(shù)據(jù)初始化為數(shù)據(jù)位8位,停止位1位,無奇偶校驗(yàn)位,波特率為115.2kB/s,在完成上電BIT后,主機(jī)可通過改變雙口存儲(chǔ)器的初始化參數(shù)來滿足自身對(duì)串行數(shù)據(jù)格式的約定,16C554各寄存器地址分配如表3所示,各個(gè)寄存器對(duì)應(yīng)的訪問地址為該串行通道分配的基地址加上偏移地址,即:各寄存器訪問地址=BASE+[A2A1A0]16。

串行協(xié)議芯片通過有效的初始化才能實(shí)現(xiàn)串行數(shù)據(jù)的正確接收和發(fā)送,在進(jìn)行初始化的時(shí)候確保串行通道沒有接收和發(fā)送數(shù)據(jù)。其初始化流程如表4所示。

1.4 控制邏輯電路

控制邏輯電路負(fù)責(zé)整個(gè)DSP數(shù)據(jù)處理模塊上控制和狀態(tài)信號(hào)的產(chǎn)生,負(fù)責(zé)PCI總線時(shí)序控制和邏輯譯碼。該邏輯功能由CPLD可編程邏輯器件實(shí)現(xiàn),邏輯描述由VHDL語言完成。控制邏輯電路主要完成以下功能:

(1)TMS320F2812總線時(shí)序支持電路;

(2)系統(tǒng)總線接口時(shí)序支持電路;

(3)地址譯碼;

(4)地址轉(zhuǎn)換及地址三態(tài)控制;

(5)實(shí)現(xiàn)對(duì)數(shù)據(jù)總線管理邏輯的控制;

(6)系統(tǒng)總線復(fù)位。

2 結(jié)束語

根據(jù)以上原理,我們研制了本智能接口板,其通用性強(qiáng),接口簡單,可以滿足大多數(shù)應(yīng)用條件,經(jīng)使用證明設(shè)計(jì)合理,穩(wěn)定可靠。

評(píng)論