基于DSP TMS 3 2 0F2 8 1 2的智能接口板設計

雙端口RAM芯片有兩套完全獨立的數據線、地址線和讀寫控制線,因而可使兩個處理器分時獨立訪問其內部RAM資源。由于兩個CPU同時訪問時的仲裁邏輯電路全部集成在雙端口RAM內部,因而需要實際設計的電路比較簡單。雙端口RAM內一般都有一個總線搶占優先級比較器,只要雙CPU不同時訪問同一存儲單元,那么較先送出地址的CPU將擁有該單元的本次訪問優先權,而另一個CPU的地址與讀寫信號將被屏蔽掉,同時通過busy引腳告知該CPU以使之根據需要對該單元重新訪問或撤銷訪問。

共享存儲器選用雙口內存IDT7027,存儲容量為32k×16bit。共享存儲器具有兩組獨立的地址、控制、I/O引腳,允許從任一組引腳發出的信號對內存中的任何位置進行讀或寫的異步訪問。雙口內存IDT7027具有防止雙口競爭的功能,該功能可以免去為避免雙口競爭增加的硬件邏輯,通過使用芯片上的信號量可以獲得芯片的控制權,只有獲權的一組引腳上的信號才能訪問內存,另外通過信號量的使用還可以將雙口內存劃分為大小不同的區。

在此模塊設計中,雙口存儲器一邊由DSP處理器控制,另一邊由PCI總線進行控制,而芯片本身自帶的BUSY通過邏輯設計接READY來實現雙口存儲器產生競爭時的應答。

·雙口存儲器讀操作訪問

雙口存儲器的讀操作時序如圖3所示,/CE為讀寫數據操作的片選信號,低電平有效;/OE為輸出控制信號,由系統讀信號控制,低電平有效;/UB、/LB是高/低字節有效控制信號,低電平有效,設計中將這兩信號下拉;R/*W信號在讀操作中保持高電平。本文引用地址:http://www.104case.com/article/150897.htm

·雙口存儲器寫操作訪問

雙口存儲器的寫操作時序如圖4所示,/CE為寫數據操作的片選信號,低電平有效;/UB、/LB是高/低字節有效控制信號,低電平有效,設計中將這兩信號下拉;R/*W為輸入控制信號,由系統寫信號控制,低電平有效。

·雙口存儲器BUSY,信號使用及時序

A/B通道對雙口存儲器的某一個單元同時進行訪問時會出現競爭風險,要避免這種情況的出現必須對訪問信號判斷優先級,IDT7025雙口存儲器通過自身硬件的BUSY信號引腳告知該CPU以使之根據需要對該單元重新訪問或撤消訪問,其操作時序如圖5所示,BUSY信號低電平有效,R/W為讀寫信號。

1.2 時鐘和復位電路

1.2.1 時鐘電路

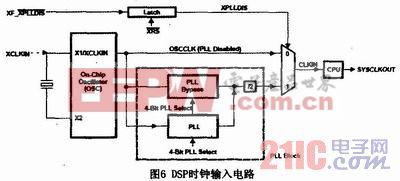

F2812處理器上有基于PLL的時鐘模塊,為器件及各種外設提供時鐘信號。鎖相環有4位倍頻設置位,可以為處理器提供各種頻率的時鐘。時鐘模塊提供兩種操作模式,如圖6所示。

內部振蕩器:如果使用內部振蕩器,則必須在x1/XCLKIN和X2引腳之間連接一個石英晶體;

外部時鐘:如果使用外部時鐘,可以把時鐘信號直接接到X1/XCLKIN引腳上,X2懸空。

外部XPLLDIS引腳用來選擇系統時鐘源。當XPLLDIS為低電平時,系統直接采用外部時鐘作為系統時鐘;當XPLLDIS為高電平時,外部時鐘經過PLL倍頻后,為系統提供時鐘。系統通過鎖相環控制寄存器來選擇鎖相環的工作模式和倍頻系數,如表2所示。

評論