基于Virtex-5的PCI-Express總線接口設計和實現

4 實驗結果分析

首先初始化FPGA內部的寄存器文件,通過設置相應的控制位啟動數據從Host內存通過PCI-Express接口向下傳輸到FPGA內部,傳輸完畢后,FPGA內部控制邏輯將接收的數據進行處理,并得到向上輸出的數據,然后通過PCI-Express接口,再將數據傳輸回Host內存,Host內存的檢測程序對所收到的數據進行校驗。在進行FPGA內部PCI-Express接口速度測試時,由于Host讀寫內存需要一定的時間,所以在測試速度時不進行Host內存的讀寫。而在正確性測試時,則通過Host讀寫內存判斷數據是否正確。所有ChipScope截圖均以一包數據包大小為4KDW為例進行捕捉,圖中有文字標識其中的信號意義。

圖6為Host將數據通過PCI-Express接口向下傳輸到FPGA內部的ChilpScope截圖。本文引用地址:http://www.104case.com/article/150893.htm

從圖中可以看出,FPGA接收數據包的最大載荷為512B,而發送數據包為128B。在Host將數據通過PCI-Express接口向下傳輸到FPGA過程中,首先FPGA要向Host發送一系列mem讀請求包,Host收到請求包后,就根據請求包的內存地址和數據長度發送CPLD包給FPGA,FPGA解析CPLD包并存儲數據到相應數據區。圖7為在Windows XP下測得的每包數據包大小為16KDW時傳輸速率為5.03Gb/s。

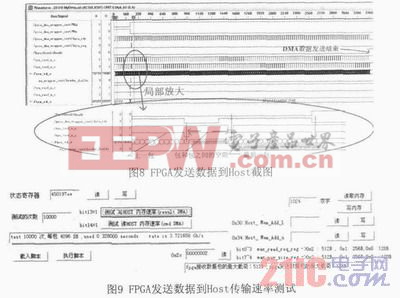

圖8為FPGA處理完后將數據通過PCI-Express接口向上傳輸到Host的ChipScope截圖。從圖中可以看出包和包之間的發送有一定的間隔,這是因為控制每包發送造成的間隔,所以在同樣每包數據包大小為16KDW時測得的傳輸速率要底于Host向下傳輸的速率,只有3.7Gb/s左右。

5 總結和展望

Virtex5系列FPGA芯片內嵌PCI-Express End-pointBlock硬核,為實現單片可配置PCI-Express總線解決方案提供了可能。基于Virtex5 FPGA的PCI-Express設計實現方式簡單、配置靈活,適合于各種應用領域,降低了設計成本,縮短了產品上市時間,保證了產品的功能性和易用性,開創了高效率PCI Express開發的新時代。

評論