基于Virtex-5的PCI-Express總線接口設計和實現

3 PCI-Express總線接口設計

本文的硬件主要就是單片XC5VLX50T實現PCI-Express總線接口,并在該FPGA內設計具體應用,完成PCI-Express總線接口的測試和使用。本文實現的應用有如下幾個特性:

(1)主機通過控制FPGA內部的寄存器文件來啟動和停止DMA操作,支持endpoint到root的全雙工DMA讀寫。

(2)使用LogiCORE產生的Endpoint Block Plus進行PCI-Express總線接口設計。該硬核集成了PCIE協議中的物理層、數據鏈接層的解析,提供傳輸層接口(TRN)供設計者對相應的事務層數據包的處理。

(3)PCI-Express總線接口支持x4通道的實現,主機操作系統為嵌入式Linux 2.6.10系統。在Windows XP下也進行PCI-Express接口測試。

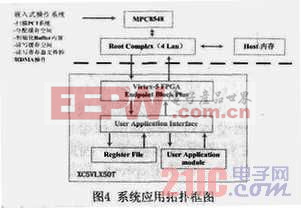

FPGA是整個設計的最關鍵部分,主要實現:PCI-Express硬核;在硬核的用戶接口和傳輸接口實現PCI-Express傳輸本地總線的時序邏輯;并且在其內部完成DMA控制時序邏輯。FPGA是PCI-Express總線接口和應用模塊數據傳輸的通道。在Host端使用嵌入式的MPC8548作為主機系統應用CPU,設計相應的驅動和應用程序配合FPGA內部代碼的調試。圖4為該系統的拓撲框圖。本文引用地址:http://www.104case.com/article/150893.htm

使用LogiCORE產生的Endpoint Block Plus中,定義了兩個基地址memory空間,一個用于DMA寄存器的操作,一個用于用戶邏輯空間。本文主要介紹的就是用戶應用層接口的實現,該接口將通過TRN進行相應的事務層數據包的處理。

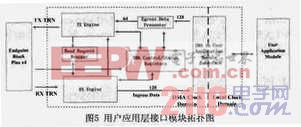

用戶應用層接口主要包括如下幾個模塊:a.TX Engine模塊;b.RX Engine模塊;c.Egress Data Presenter模塊;d.Read Request Wrapper模塊;e.DMA Control/Status Registers模塊。這幾個模塊之間的拓撲關系如圖5所示。

TX Engine:該模塊主要用于產生和發送事務層數據包:Posted事務包(存儲器、I/O、配置讀寫事務)、non_Posted事務包(該總線事務包分兩步進行,首先是發送端向接收端提交總線讀寫請求,之后接收端再向發送端發送完成包)和completion(完成)包。該模塊通過發送posted memory寫,non_Posted memory讀,和接收completion包來完成DMA的讀寫請求。該模塊的啟動由DMA Control/Status Registers模塊控制。該模塊又包括若干子模塊:posted packet generator模塊、non posted packet generator模塊、completion packet generator模塊和transmit TRN state machine模塊,上述三個generator模塊均由transmit TRN狀態機模塊控制,該狀態機的控制信號來自Endpoint Block Plus核以及DMA Control/StatusRegisters模塊。

RX Engine:該模塊主要用于接收Endpoint BlockPlus模塊從RX TRN接口送出的事務層數據包,對不同的事務包進行解析,根據相應的包做相應的處理,該模塊能處理如下三種事務包:完成包、memory讀包和memory寫包。該模塊又包括如下子模塊:接收TRN狀態機模塊、接收TRN監控模塊、接收數據狀態機模塊以及兩個fifo用于存放完成包的接收數據和完成包中目的和源的地址以及數據包的長度,用于設置DMA Control/Status Registers模塊中的各個狀態。接收TRN狀態機模塊只負責TRN接口處的數據包的狀態和接收收據,送給后面的模塊;接收TRN監控模塊負責根據不同的TLP包來分配數據和狀態,是直接將帶數據的完成包的數據寫到用戶應用接口fifo,還是讀請求或寫請求TLP包通知TX engine,組成相應的包發送出去或者通知DMA控制器進行相應的DMA傳送控制;接收數據狀態機模塊對接收到的數據進行相應的處理。

Egress Data Presenter:該模塊是專門為TX Engine模塊提供發送數據的模塊,要發送到主機的數據都在該模塊中進行處理,它和TX Engine模塊間的數據位寬定義為64bit。

Read Request Wrapper:該模塊主要用于TX Engine模塊和RX Engine模塊之間的通信控制接口,本文中設計DMA的讀寫操作每包可能的數據長度為:1KDW、2KDW、3KDW、4KDW、8 KDW、16 KDW之間可選。該選擇是由主機通過寫寄存器文件來進行長度策略選擇的。

DMA Control/Status Register:該模塊主要用于主機系統通過控制FPGA內部的寄存器文件的設置來啟動和停止endpoint到root的DMA讀寫操作。包括一個控制寄存器以及若干個配置寄存器,配置寄存器有主機的目的地址、源地址信息,本地的目的地址、源地址信息,以及每次DMA的數據包長度等信息。由控制寄存器中的bit位的狀態來啟動所有的狀態機的控制,所以控制寄存器是整個操作的關鍵信號。

評論