基于DSP的過采樣技術(shù)的應(yīng)用

1 引言

本文引用地址:http://www.104case.com/article/150717.htm模數(shù)(AD)轉(zhuǎn)換通常是數(shù)字信號(hào)處理應(yīng)用中的第一步,依據(jù)應(yīng)用的不同,對模數(shù)轉(zhuǎn)換器(ADC)也有不同的要求,衡量模數(shù)轉(zhuǎn)換器的最重要的標(biāo)準(zhǔn)是它的轉(zhuǎn)換速率、分辨率和精度。因此,使用過采樣技術(shù),再加上適當(dāng)?shù)臄?shù)字濾波和抽取,就可以得到比原有的ADC更高的分辨率。

在數(shù)字信號(hào)處理器(DSP)中應(yīng)用過采樣技術(shù)需要快速ADC以非常快的速度來采樣模擬信號(hào),并且需要快速DSP來執(zhí)行數(shù)字低通濾波和抽取。TI公司出品的DSP芯片TMS320LF2407采用3.3V供電,30MIPS的執(zhí)行速度使得指令周期縮短至33ns,內(nèi)置有10位的AD轉(zhuǎn)換器,最小轉(zhuǎn)換時(shí)間為500ns,這些為在DSP中應(yīng)用過采樣技術(shù)創(chuàng)造了條件。

2 過采樣降低對模擬抗混疊濾波器的限制

在采樣過程中首要的問題是采樣頻率的選擇,NyquiST采樣定理指出:若連續(xù)信號(hào)x(t)是有限帶寬的,其頻譜的最高頻率為fc,對x(t)采樣時(shí),若保證采樣頻率fs≥2fc,那么,就可由采樣信號(hào)恢復(fù)出x(t)。在實(shí)際對x(t)作采樣時(shí),首先要了解x(t)的最高截止頻率fc,以確定應(yīng)選取的采樣頻率fs。若x(t)不是有限帶寬的,在采樣前應(yīng)使用抗混疊(anti-aliasing)濾波器對x(t)作模擬濾波,以去掉f>fc的高頻成分。

因此,在AD轉(zhuǎn)換前就需要模擬低通濾波器具有尖銳的滾降特性,來限制模擬信號(hào)的頻譜。一個(gè)理想的濾波器應(yīng)能讓所有低于fs/2的頻率通過,而完全阻隔掉所有大于fs/2的頻率。通常,濾波器和采樣頻率的選擇是將我們感興趣的頻帶限制在DC和fs/2之間。

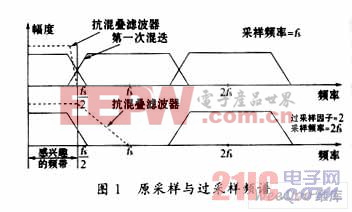

用更高的采樣頻率可以降低對低通濾波器的限制,圖1所示為以2倍的原采樣頻率對模擬信號(hào)進(jìn)行采樣,在這種情況下,濾波器的截頻為fs/2,阻帶的起始頻率為fs,這樣就可以讓所有我們感興趣的頻率通過,而抑制掉所有高于fs的頻率。但這樣做違反了Nyquist采樣定理,所以還需要用ADC后的數(shù)字濾波器來將信號(hào)的頻率限制到fs/2以下。采用了過采樣后的這種抗混迭濾波器可以得到簡化,允許的通帶到阻帶的過渡區(qū)很寬。

3 過采樣提高信噪比

經(jīng)模擬濾波后,模擬信號(hào)被采樣并轉(zhuǎn)換成數(shù)字值,因?yàn)閿?shù)字域僅包含有限的字長,若要用它來表示連續(xù)信號(hào),就要引入量化誤差,最大量化誤差為±0.5LSB。因?yàn)橐粋€(gè)N位的ADC的輸入范圍被分成2N個(gè)離散的數(shù)值,每一個(gè)數(shù)值由一個(gè)N位的二進(jìn)制數(shù)表示,所以,ADC的輸入范圍和字長N是最大量化誤差的一個(gè)直接表示,也是分辨率的一個(gè)直接表示。代表數(shù)字值的字長決定了信噪比,因此通過增加信噪比可以增加轉(zhuǎn)換的分辨率。加入三角波信號(hào)可提高信噪比(詳見TI公司的資料:Oversampling techniques Using theTMS320C24x Family,June 1998)。

如果輸入信號(hào)在兩個(gè)量化步長q1與q0之間,則它將被量化成q1或q0。當(dāng)增加一個(gè)適當(dāng)?shù)娜遣ㄐ盘?hào),并高速采樣,將會(huì)量化出一系列的q1與q0,這兩個(gè)值出現(xiàn)的比例就代表了此輸入信號(hào)在兩個(gè)量化步長之間的相對位置。要應(yīng)用這種方法得到比較好的效果,三角波信號(hào)的幅度必須為(n+0.5)LSB,其中,n=0,1,2,…

因?yàn)橛辛烁卟蓸铀俾剩斎胄盘?hào)的變化相對來說比較緩慢,圖2中,輸入信號(hào)為0.6 LSB,一個(gè)典型的AD轉(zhuǎn)換器將采樣這個(gè)信號(hào)并把它轉(zhuǎn)換成1 LSB。當(dāng)用一個(gè)三角波信號(hào)與此輸入信號(hào)進(jìn)行疊加,并高速采樣時(shí),轉(zhuǎn)換器產(chǎn)生一系列的0或1采樣值。0和1出現(xiàn)的比例就表示了這個(gè)在0和1 LSB之間的實(shí)際值。

評論