FPGA在鎖相頻率合成中的應用

累加器采用BCD碼全加器。如要實現六位小數分頻,每級累加器需三個八位鎖存器和六個BCD碼全加器。為了使電路設計相對簡單,調制器部分采用吞脈沖技術。在采用三級累加器的情況下(參見圖2),分頻比最小時為N-3(第二級累加器-1有效,第三級累加器-2有效),最大時為N+4(圖中三級累加器+1均有效)。因為是采用吞脈沖技術(不能添加脈沖),即在分頻比為N-3時吞掉的脈沖最少。因此,在累加器全無溢出的情況下(分頻比為N),應吞掉三個以上的脈沖,而這本不應吞掉的脈沖在整數分頻部分予以添加。本設計采用無溢出時吞4個脈沖的方法,在三級調制器中的累加器的所有輸出情況下會吞掉1~8個脈沖。整數分頻計數器實際計數溢出值比分頻值小4,以添加本不應吞掉的4個脈沖。

3 ∑-Δ調制器的FPGA實現

FPGA是80年代中期出現的高密度可編程邏輯器伯。FPGA及其系統軟件是開發數字集成電路的最新技術,它利用計算機輔助設計,以電路原理圖、高級語言、狀態機等形式輸入設計邏輯;它提供功能模擬、定時模擬等模擬手段,在功能模式、定時模擬都滿足要求后,經過一系列的變換,將輸入邏輯轉換成FPGA器件的編程文件,以實現專用集成電路。

上述∑-Δ調制器采用三級累加器,實現六位小數分頻。采用74系列的電路,需要約60片左右的集成芯片,電路板尺寸比較大,電路調試麻煩,可靠性差,很難推廣使用和形成產品。將∑-Δ調制器用FPGA器件來實現,不但電路體積大大縮小,而且可靠性大大提高。使用FPGA器件的另一個好處是,可將同一系統中的其它數字電路納入其中進一步縮小體積。

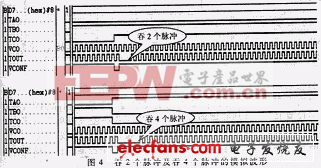

本設計的軟件環境為Xilinx公司Foundation Serials 1.5i。采用原理圖輸入的設計方法,將復雜的原理圖分塊放在同一設計項目中,輸入完畢后進行功能模擬,確認功能正確以后,對原理圖進行編譯并進行FPGA器件內部的布局布線,同時生成定時模擬數據文件。功能模擬主要是驗證三級∑-Δ調制器的功能是否正確,判斷的依據是看其是否可實現吞掉1~8個脈沖。圖4是功能模擬的部分波形圖,采用XC3064A-7-PC84芯片對設計進行布局布線,結果使用資源情況為CLB86%、IOB 27%、GCLK被使用。最高工作頻率為4MHz。定時模擬能夠保證功能正確。

在本設計中,將整數分頻電路、吞脈沖電路均做在FPGA器件之中,進一步減小了電路板尺寸。

分頻器相關文章:分頻器原理

評論