VHDL語言在FPGA/CPLD開發中的應用?

【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

關鍵詞:VHDL,FPGA/CPLD,EDA

1 引 言

EDA(電子設計自動化)關鍵技術之一是采用硬件描述語言(HDL)描述電路系統,包括電路結構、行為方式、邏輯功能以及接口。就FPGA和CPLD(分別是現場可編程門陣列和復雜可編程邏輯器件的簡稱)開發來說,比較流行的HDL主要有VHDL、ABEL-HDL、AHDL等,其中,VHDL對系統的行為描述能力最強,已被IEEE確定為標準HDL,并得到目前所有流行EDA軟件的支持,進而成為系統設計領域最佳的硬件描述語言。用VHDL設計電路系統,可以把任何復雜的電路系統視為一個模塊,對應一個設計實體。在VHDL層次化設計中,它所設計的模塊既可以是頂層實體,又可以是較低層實體,但對不同層次模塊應選擇不同的描述方法(如行為描述或結構描述)。本文在設計實例中詳細介紹了用VHDL語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

2 設計實例

一個復雜電路系統的設計都是采用自頂向下將系統按功能逐層分割的層次化設計方法。在頂層設計中,要對內部各功能塊的連接關系和對外的接口關系進行描述,而功能塊實際的邏輯功能和具體的實現形式則由下一層模塊來描述。在系統的底層設

計中,如采用VHDL進行描述,由于其對系統很強的行為描述能力,可以不必使系統層層細化,從而避開具體的器件結構,從邏輯行為上直接對模塊進行描述和設計,之后,EDA軟件中的VHDL綜合器將自動將程序綜合成為具體FPGA/CPLD等目標芯片的網表文件,無疑可使設計大為簡化。下面以數字鐘的設計為例予以說明。

數字鐘的功能主要有:

·能夠對秒、分、小時進行計時(按每日24小時計時制)。

·秒、分、小時位能夠調整。

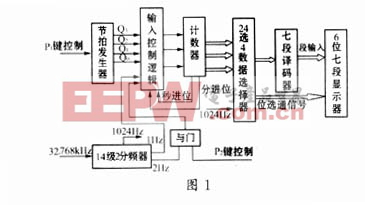

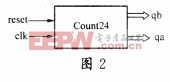

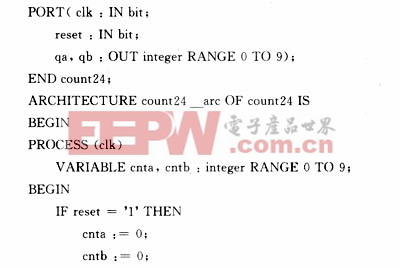

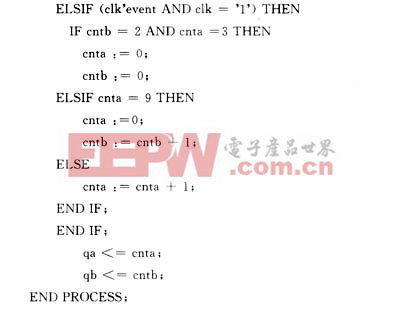

根據數字鐘的功能要求,可將數字鐘分為四個功能塊:秒脈沖發生器、計數器、校時器和顯示電路。而這些功能塊又可進一步分割為更小的模塊,如計數器模塊可再分為秒、分、小時計數器。其它功能塊的細化過程不再詳述,數字鐘的系統框圖如圖1所示。圖中,P1鍵為自動計時、校時、校分和校秒四種工作狀態選擇鍵,P2鍵為系統處于校時狀態時對時、分、秒進行校準的校時鍵,32.768kHz為作為脈沖源的晶振頻率,經14級2分頻器分頻在其最高位、次高位以及第五位輸出端分別可獲得1Hz、2Hz和1024Hz的脈沖信號,這三個脈沖信號分別用作計時脈沖、校時脈沖和顯示電路的掃描時鐘。下面用VHDL語言設計底層的小時計數器。小時計數器為一個24進制BCD碼計數器,其模塊示意圖如圖2所示。reset、clk分別為異步清零端和時鐘端,qb和qa分別為十位和個位的四位BCD碼輸出端。該模塊計數方式的實現比較復雜,當十位數為0或1時,個位進行10進制計數,當十位數為2時,個位進行4進制計數。如用電路圖描述,則必須選擇和調用若干門、觸發器或宏單元,并需對所調用的器件進行合適的控制。而若采用VHDL語言對其功能進行描述,問題則顯得非常簡單。

評論