基于DSP的高階COSTAS鎖相環的設計

3.1 SIN/COS函數的查表算法

為了提高算法的實現效率,介紹運行時計算的時間開銷,應盡可能把一些運行時計算的參數做成查找表或常數數值。這不僅適用于一些比較規整的參數表,對于一些并不規整的運行時的計算,例如上下變頻和VCO中,用到與載波相乘的SIN/COS的計算,可以采用寫成數組,用查表來實現。

3.2 運算的流水處理

DSP的CPU多采用流水線結構。DSP的大多數指令為單周期指令,而跳轉類指令卻通常要耗費較多的機器周期。可以將多重循環拆開,減少對外層循環次數進行控制轉移的時間,充分利用優化器構成的流水線。

3.3 CIC梳狀濾波器的使用

利用CIC濾波器代替低通濾波器,達到減少定點乘法和加法運算的目的,解決了單片C6416資源不足的問題。例如:本文中載波速率為4800kHz,采樣率為230.4kHz,鑒相器輸出的高頻頻率為9600kHz,采用48階CIC可以將9600kHz的頻率分量濾掉。由于在 的位置,因此濾除效果非常好,遠大于 。CIC濾波器每項系數都是1,利用加法運算可以實現需要大量乘法和加法運算的功能,減少對DSP片內資源的使用。

3.4數據傳輸的EDMA方式

在調制解調過程中,DSP和外部之間存在大量數據的交換,這部分的優化工作影響系統性能。C64x支持EDMA,EDMA是增強型DMA,是一種在沒有CPU介入情況下的訪問存儲器的方式,即由EDMA控制器控制數據在L2內存/緩存和片內集成外設及片外設備之間的傳輸,而同時CPU可以并行的執行其它指令。EDMA是一種有效的數據傳輸方式,可以有效的減少EMIF在CPU下操作需要的資源。

具體實現方法如下:在片內數據存儲區定BUF的長度,并一分為二,可設為BUF1和BUF2。在EMDA里BUF1和BUF2都是等存儲大小的。在數據幀同步信號的上升沿,DSP以EDMA的方式從外部讀一幀的數據到BUF1;同時BUF2內的數據進行MPSK的解調算法。同理,在下一個數據幀同步信號的上升沿,DSP以EDMA的方式從外部讀另一幀的數據到BUF1 。BUF1讀滿后,DSP對BUF1內的數據進行MPSK的解調算法,同時BUF2進行數據的讀操作,實現EDMA的乒乓處理。

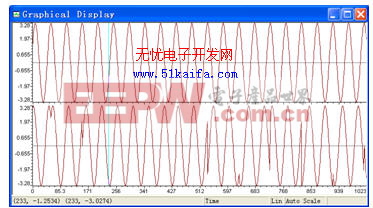

本文選取8PSK的符號速率為2400kbps,載波速率為4800kHz,采樣率為230.4kHz。圖2所示的兩路信號分別是利用CCS開發工具的觀察窗口觀察到的,提取的同頻同相的載波信號和8PSK的調制信號。

圖3 恢復的載波信號(上)和接收到的基帶信號(下)

圖4 8PSK接收端解調前星座圖(AWGN信道,SNR=17dB)

5. 結束語

本文主要介紹了一種新型的適用于MPSK載波提取的高階COSTAS環路,能滿足MPSK相干解調的需要,且便于DSP實現。針對COSTAS環算法的DSP實時實現問題,進行了詳細的討論。最后,針對一個具有較高數據速率8PSK調制解調實例,在單片C6416上完成了基于高階COSTAS環的載波同步及相干解調,并給出了通過CCS工具觀察到的DSP實現結果,證明高階COSTAS鎖相環具有較好的載波同步性能。

低通濾波器相關文章:低通濾波器原理

鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論