JPEG2000中位平面編碼的存儲優化方案設計

4.Verilog設計

本文建議的硬件架構采用VERILOG[4]語言描述,主模塊是bpc.v,包括ram_block.v,addr_generator.v,fill_ram.v,pass_judge.v,coding_primitive.v和state_machine.v共6 個子模塊。編碼流程的實現通過主狀態機產生相應的使能信號,激活當前的模塊操作,當操作完成后,由該模塊產生操作中止信號給主狀態機,從而使編碼流程進入下一步驟。下面列出了部分用于模塊間握手的代碼,代碼中以省略號代表其它一些控制信號和其它一些狀態。

case (cstate)

。。。

gene_layer:begin

。。。gene_layer_en = 1;fill_ram_en = 0;pass_judge_en = 0; 。。。

if (gene_layer_fin) nstate = fill_ram;else nstate = gene_layer;end

fill_ram:begin

。。。gene_layer_en = 0;fill_ram_en = 1;pass_judge_en = 0; 。。。

if (fill_ram_fin) nstate = pass_judge;else nstate = fill_ram;end

。。。

endcase

5.實驗結果

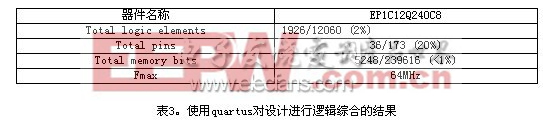

本設計采用modelsim工具進行了功能仿真,使用quartus[6]工具進行了邏輯綜合,得到的綜合結果如表3所示。

下面是使用jasper軟件和本硬件實現對幾幅標準圖像(大小512×512的灰度圖像)編碼的時間比較。

6.結論

本文通過對JPEG2000中的位平面編碼器的存儲方案進行了分析,設計了一個高效的存儲結構以及相應的控制電路,設計采用verilog[4]語言描述,通過quartus[6]軟件邏輯綜合后,能夠在0.1s內完成一幅512×512灰度圖像的編碼,編碼時間僅為jasper[3]軟件實現方案的30%左右。由于塊編碼器的特點,每個碼塊的編碼本身是獨立的,可以并行進行,而且根據綜合結果,使用EP1C12Q240C8完全可以在一塊芯片內集成多個位平面編碼器的IP核,每個塊編碼器核可以并行執行,因此,可以進一步提高編碼器的速度,從而使實時處理圖像成為可能。另外,還可以將設計定制為ASIC,將最終產品應用到數碼相機、圖像監控中,其市場前景是十分廣闊的。

評論