基于FPGA PCI的并行計(jì)算平臺(tái)實(shí)

本文介紹的基于PCI總線的FPGA計(jì)算平臺(tái)的系統(tǒng)實(shí)現(xiàn):通過在PC機(jī)上插入擴(kuò)展PCI卡,對(duì)算法進(jìn)行針對(duì)并行運(yùn)算的設(shè)計(jì),提升普通PC機(jī)對(duì)大計(jì)算量數(shù)字信號(hào)的處理速度。本設(shè)計(jì)采用5片FPGA芯片及相關(guān)周邊芯片設(shè)計(jì)實(shí)現(xiàn)這一并行高速計(jì)算平臺(tái),并在該平臺(tái)上完成了DES和MD5等算法的加密和解密。文中通過基于MD5算法設(shè)計(jì)的加密方案(仿Yahoo郵箱的密碼校驗(yàn))進(jìn)行暴力破解,驗(yàn)證了本系統(tǒng)的可行性以及速度快、性價(jià)比高等顯著優(yōu)點(diǎn)。

本文引用地址:http://www.104case.com/article/150290.htm1 系統(tǒng)結(jié)構(gòu)

系統(tǒng)利用普通PC機(jī)或工控機(jī)進(jìn)行控制、數(shù)據(jù)流下載和結(jié)果采集,大計(jì)算量的數(shù)字運(yùn)算利用IP-CORE技術(shù)并行地在FPGA中進(jìn)行。將數(shù)字信號(hào)處理的算法設(shè)計(jì)為一個(gè)單元模塊,并根據(jù)芯片的結(jié)構(gòu)對(duì)布局和布線進(jìn)行優(yōu)化,該單元模塊重復(fù)利用的技術(shù)被稱為IP-CORE技術(shù)。在本系統(tǒng)中利用TP-CORE的可重復(fù)利用性,通過仲裁邏輯調(diào)度數(shù)據(jù)的分配,從而實(shí)現(xiàn)算法的并行處理。

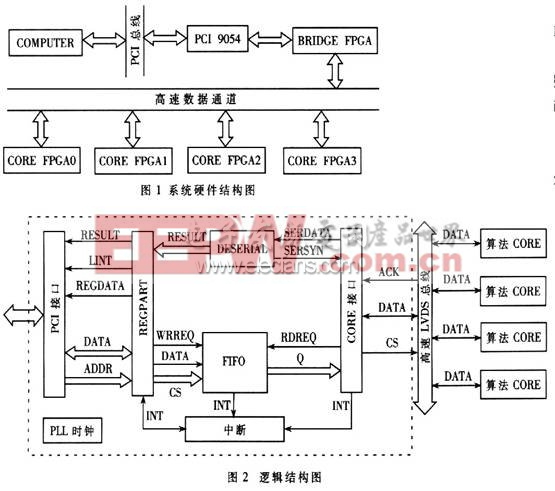

1.1 硬件結(jié)構(gòu)

系統(tǒng)中采用5片ALTERA公司的STRATIX EP1Sl0FPGA芯片,其中4片作為數(shù)字信號(hào)處理算法CORE的載體(文中稱為算法FPGA);l片作為連接PC機(jī)與運(yùn)算CORE的橋接芯片、加載程序、并行總線裁決和中斷判決等仲裁邏輯的載體。與PCI總線的接口使用PLX公司的PCI9054芯片。系統(tǒng)硬件結(jié)構(gòu)如圖l所示。

1.2 邏輯結(jié)構(gòu)

1.2 邏輯結(jié)構(gòu)BRIDGE FPGA的程序采用自頂向下的設(shè)計(jì)方法,其邏輯結(jié)構(gòu)如圖2所示,按功能可分為以下部分:頂層模塊PCI_FPGA_PARALLEL;與PCI9054的接口模塊PCI接口;數(shù)據(jù)緩存及仲裁部分:數(shù)據(jù)緩存模塊FIFO、寄存器模塊regpart、數(shù)據(jù)回傳模塊deserial、內(nèi)部總線仲裁和流控模塊CORE接口等。

PCI接口部分實(shí)現(xiàn)與PCI9054芯片的接口時(shí)序,使得復(fù)用的地址和數(shù)據(jù)分開,產(chǎn)生地址空間的選取及使能信號(hào),便于后端處理。

仲裁邏輯部分:

(1)實(shí)現(xiàn)對(duì)地址空間內(nèi)數(shù)據(jù)緩沖區(qū)、各種寄存器的讀寫,以及根據(jù)配置寄存器的內(nèi)容對(duì)算法CORE和橋FPGA做相應(yīng)的操作(配置、啟動(dòng)、停止、復(fù)位等)。

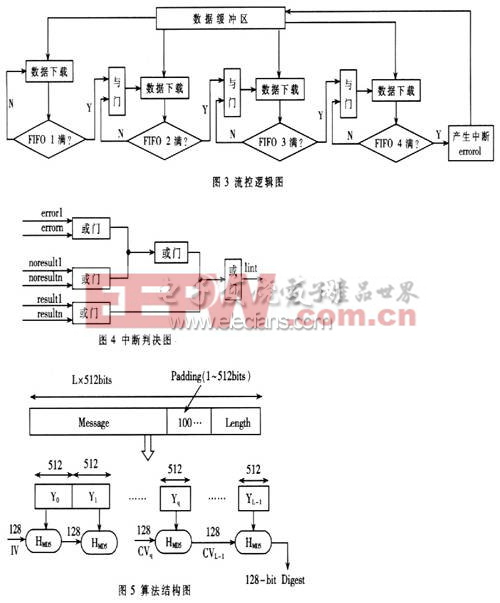

(2)利用緩沖區(qū)及FIF0的隊(duì)列長(zhǎng)度信號(hào)wrusedw、rdusedw、full和empty進(jìn)行數(shù)據(jù)流控制。數(shù)據(jù)由PC機(jī)下載時(shí)首先進(jìn)入緩沖區(qū),每一塊算法CORE均對(duì)應(yīng)一個(gè)數(shù)據(jù)下行FIFO,由FIFO當(dāng)前狀態(tài)來判定是否從緩沖區(qū)中取數(shù)。具體邏輯模型如圖3所示。

(3)返回結(jié)果引入本地中斷機(jī)制,當(dāng)有正確結(jié)果產(chǎn)生、或無正確結(jié)果但密鑰匹配完成、或系統(tǒng)異常狀態(tài),均產(chǎn)生中斷信號(hào)并填寫中斷類型寄存器,經(jīng)級(jí)聯(lián)后產(chǎn)生向PC機(jī)的中斷。中斷判決如圖4所示。

評(píng)論