現(xiàn)代FPGA設(shè)計(jì)的能源優(yōu)化方案

引言

本文引用地址:http://www.104case.com/article/150240.htm減少FPGA的功耗可帶來(lái)許多好處,如提高可靠性、降低冷卻成本、簡(jiǎn)化電源和供電方式、延長(zhǎng)便攜系統(tǒng)的電池壽命等。無(wú)損于性能的低功耗設(shè)計(jì) 既需要有高功率效率的FPGA架構(gòu),也需要有能駕馭架構(gòu)組件的良好設(shè)計(jì)規(guī)范。

本文將介紹FPGA的功耗、流行的低功耗功能件以及影響功耗的用戶選擇方案,并探討近期的低功耗研究,以洞察高功率效率FPGA的未來(lái)趨勢(shì)。

1 功耗的組成部分

FPGA的功耗由兩部分組成:動(dòng)態(tài)功耗和靜態(tài)功耗。信號(hào)給電容性節(jié)點(diǎn)充電時(shí)產(chǎn)生動(dòng)態(tài)功耗。這些電容性節(jié)點(diǎn)可以是內(nèi)部邏輯塊、互連架構(gòu)中的布線導(dǎo)線、外部封裝引腳或由芯片輸出端驅(qū)動(dòng)的板級(jí)跡線。FPGA的總動(dòng)態(tài)功耗是所有電容性節(jié)點(diǎn)充電產(chǎn)生的組合功耗。

靜態(tài)功耗與電路活動(dòng)無(wú)關(guān),可以產(chǎn)生于晶體管漏電流,也可以產(chǎn)生于偏置電流。總靜態(tài)功耗是各晶體管漏電功耗及FPGA中所有偏置電流之和。動(dòng)態(tài)功耗取決于有源電容一側(cè),因而可隨著晶體管尺寸的縮小而改善。然而,這卻使靜態(tài)功耗增加,因?yàn)檩^小的晶體管漏電流反而較大。因此靜態(tài)功耗占集成電路總功耗的比例日益增大。

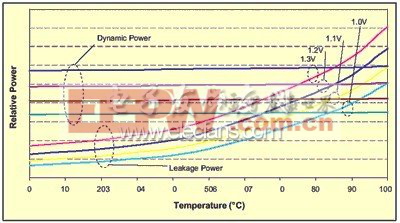

如圖1所示,功耗很大程度上取決于電源電壓和溫度。降低FPGA電源電壓可使動(dòng)態(tài)功耗呈二次函數(shù)下降,漏電功耗呈指數(shù)下降。升高溫度可導(dǎo)致漏電功耗呈指數(shù)上升。例如,把溫度從85℃升高至100℃可使漏電功耗增加25%。

圖1 電壓和溫度對(duì)功耗的影響

2 功耗分解

下面分析一下FPGA總功耗的分解情況,以便了解功耗的主要所在。FPGA功耗與設(shè)計(jì)有關(guān),也就是說(shuō)取決于器件系列、時(shí)鐘頻率、翻轉(zhuǎn)率和資源利用率。

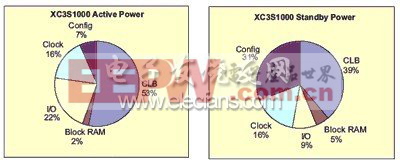

以Xilinx Spartan-3 XC3S1000 FPGA為例,假定時(shí)鐘頻率為100MHz,翻轉(zhuǎn)率為12.5%,而資源利用率則取多種實(shí)際設(shè)計(jì)基準(zhǔn)測(cè)試的典型值。

圖2所示為XC3S1000的活動(dòng)功耗和待機(jī)功耗分解圖。據(jù)報(bào)告顯示,活動(dòng)功耗是設(shè)計(jì)在高溫下活動(dòng)時(shí)的功耗,包括動(dòng)態(tài)和靜態(tài)功耗兩部分。待機(jī)功耗是設(shè)計(jì)空閑時(shí)的功耗,由額定溫度下的靜態(tài)功耗組成。CLB在活動(dòng)功耗和待機(jī)功耗中占最主要部分,這不足為奇,但其他模塊也產(chǎn)生可觀的功耗。I/O和時(shí)鐘電路占全部活動(dòng)功耗的1/3,如果使用高功耗的I/O標(biāo)準(zhǔn),其功耗還會(huì)更高。

圖2 Spartan-3 XC3S1000 FPGA典型功耗分解圖

配置電路和時(shí)鐘電路占待機(jī)功耗近1/2,這在很大程度上是偏置電流所致。因此,要降低芯片的總功耗,就必須采取針對(duì)所有主要功耗器件的多種解決方案。

評(píng)論