TMS320VC5509實現有源噪聲控制系統

由上述公式(4)可以看出,參考信號x(n)需由次級通路傳遞函數hs(n)進行濾波,所以在有源噪聲控制算法迭代之前,首先必須得到次級通路的傳遞函數。

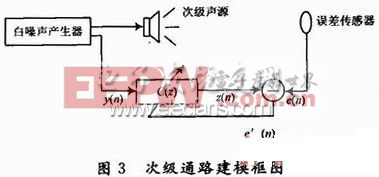

估計次級通路傳遞函數的方法稱為次級通路建模,一般有自適應離線建模和自適應在線建模兩種方法。自適應在線建模要求在有源噪聲控制系統運行的同時,對次級通路響應進行實時建模,對系統的運算能力要求較高。如果在有源噪聲控制的整個過程中,次級通路的系統特性保持不變或基本不變,就可以采用自適應離線建模方法。本系統中即采用自適應離線建模,其框圖如圖3所示。

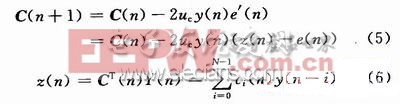

首先由DSP產生一個隨機白噪聲序列,同時送入次級聲源和自適應建模濾波器C(z),誤差傳感器接收的信號e(n)作為建模濾波器的期望信號,濾波器的輸出信號z(n)與期望信號e(n)相減抵消后,輸入建模濾波器,自動調節濾波器權系數。次級通路建模采用LMS算法,其迭代運算公式如下:

式中:uc為次級通路建模濾波器的步長因子;N為次級通路建模濾波器的階數。

實際應用中,應先關閉外部噪聲源,采用DSP隨機產生的白噪聲作為次級通路激勵源。DSP先執行次級通路濾波器的迭代,待次級通路LMS濾波器穩定后,將次級通路濾波器系數固定不變,代入上述的FXLMS濾波器進行有源消噪迭代運算。

2 系統硬件設計

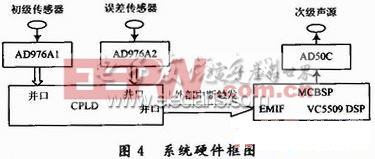

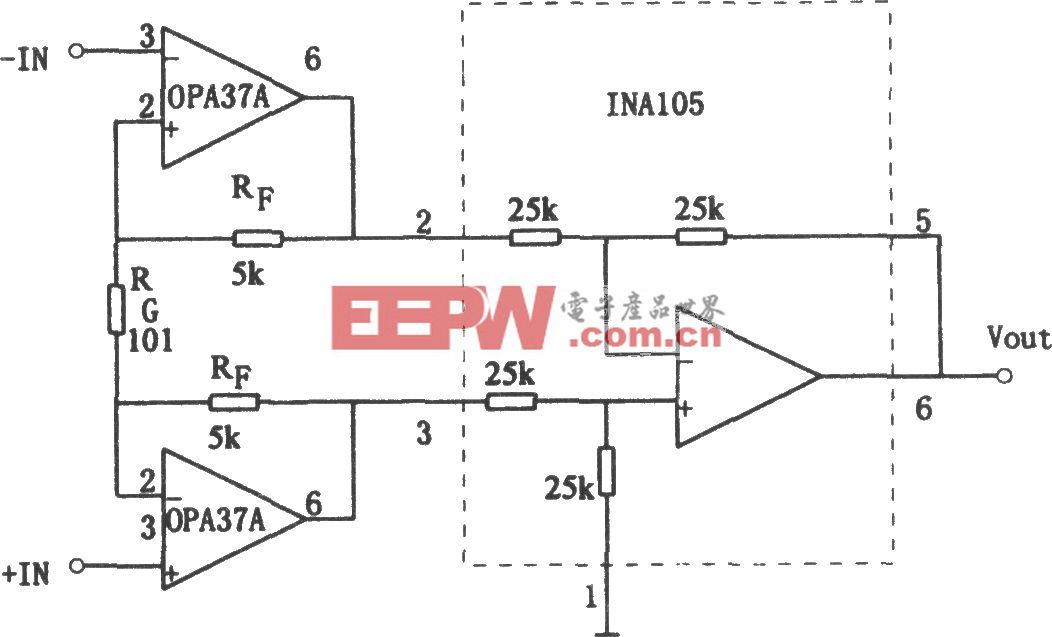

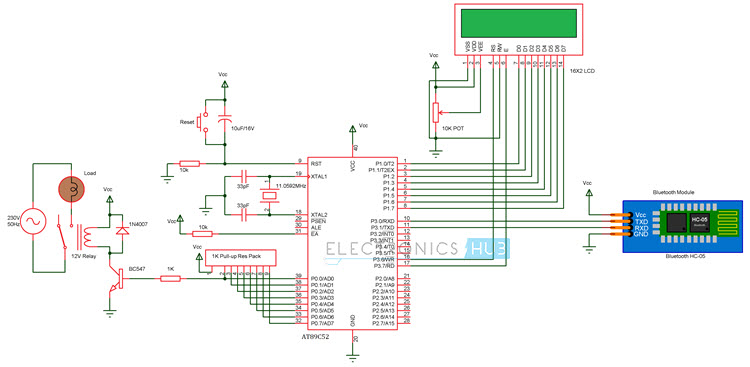

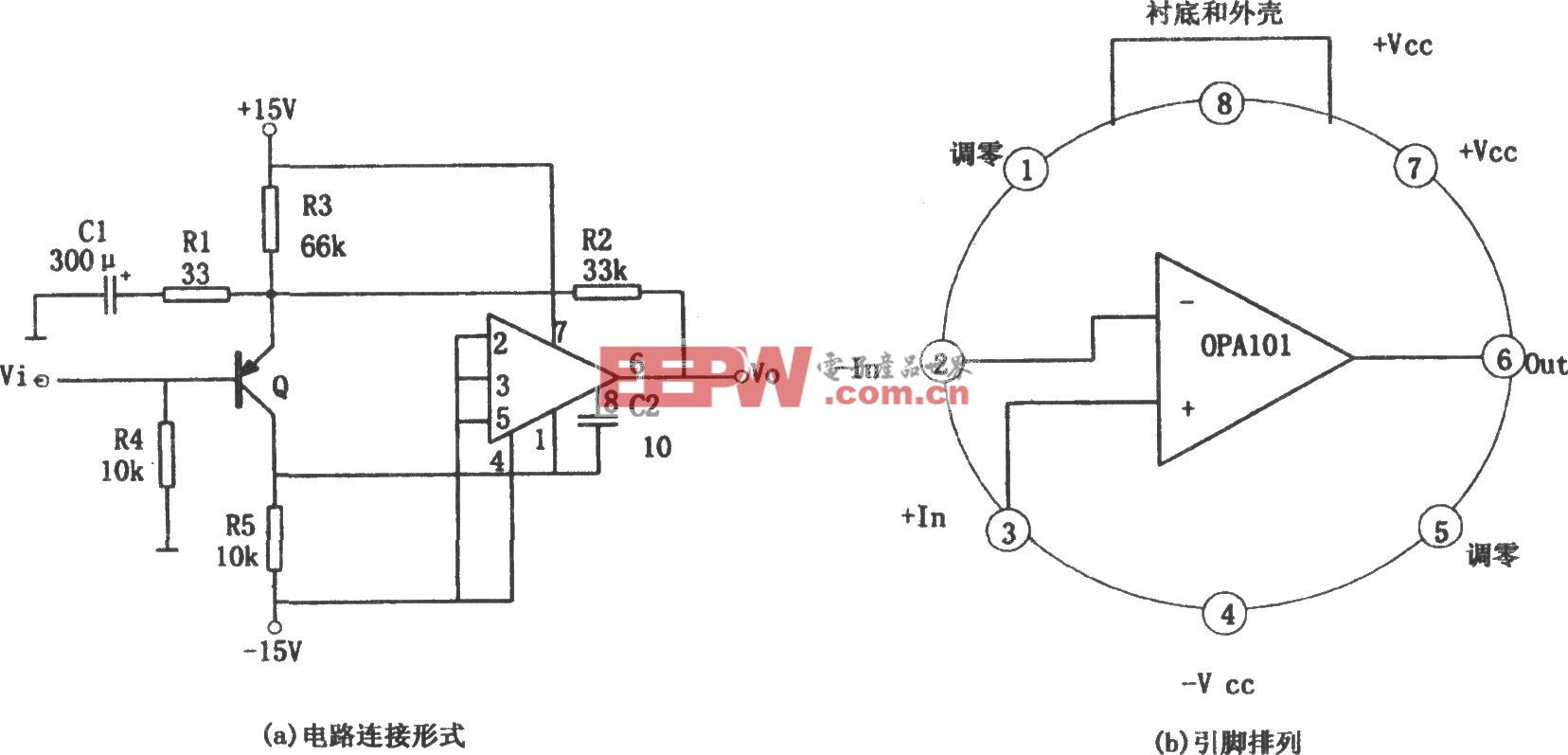

本系統為單通道前饋結構,以高速DSP芯片TMS320VC5509為核心,采用兩片16位高精度模數轉換器件AD976A實現兩路模擬信號的同步采集,并選用CPLD器件EPM7192SQC160-10設計鎖存器,以串行D/A器件AD50C完成輸出反噪聲信號的D/A轉換,選用16 Mb FLASH閃存芯片作為程序存儲器,并在片外擴充一片64 Mb SDRAM作為外部數據空間。系統硬件框圖如圖4所示。

設計選用的VC5509DSP芯片最高支持144 MHz的時鐘頻率,具有高達288 MIPS(每秒百萬條指令數)的處理能力,是一款具有較高性價比的低功耗DSP芯片。音頻接口采用的AD976A為一款高精度、高速率的并口A/D轉換器件,抽樣速率可從8~200 KSPS,抽樣速率的改變可通過改變輸入時鐘來實現,從而可實現在不改變硬件的情況下通過軟件設置進行擴展。CPLD通過編程給A/D器件提供8 kHz采樣頻率,并設計采樣保持鎖存器。經由DSP的片選引腳CE2和地址引腳A1尋址,兩個A/D轉換器的鎖存器地址分別設為0X400000和0X400001。CPLD與DSP連接圖如圖5所示。

AD50C為TI公司生產的16位可編程串行音頻接口芯片,可通過DSP編程控制收發增益和采樣頻率。其串口與DSP的同步串口連接如圖6所示。

系統信號流程如下:AD976A對噪聲參考信號x(n)和誤差信號e(n)進行8 000次/s采樣,每次采樣后由AD976A1的“BUSY”引腳觸發DSP的外部中斷4 INT4,在中斷服務程序中DSP依據地址將CPLD鎖存器中的兩個數據分別讀至內部存儲器DARAM中,進行算法運算。算出反噪聲序列y(n)后,在INT4中斷服務程序中將其送至DSP串口MCBSP0,再通過AD50C數模變換后,送往揚聲器發出反噪聲。

評論