FPGA設計當中的功耗問題研究

隨著FPGA的密度越來越高,設計者們正在節能降耗方面取得越來越多的進展。出現降低功耗這一趨勢的另一個原因是FPGA正在越來越廣泛地應用于智能手機、媒體播放器、游戲機、衛星導航設備以及數碼相機/攝像機等便攜式設備當中。對于消費電子設備以及醫療、工業,甚至軍事設備來說,功耗也許算是選擇FPGA時最重要的因素了。系統可靠性的提高和易升級性也是需要考慮的重要因素。選擇過程中的其他標準還包括成本、容量、性能、功能、功率和封裝等。

本文引用地址:http://www.104case.com/article/150118.htm浪涌功耗

配置功耗

編程后靜態功耗

動態功耗

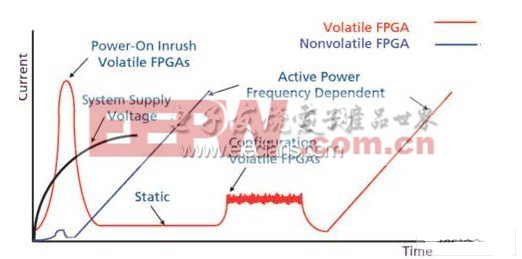

FPGA器件的功耗組成和降耗技術由于器件所采用的根本技術的差異而有所不同,比如有SRAM、混合SRAM、Flash和抗熔FPGA技術等。基于SRAM的FPGA器件包含了所有四個主要功耗組成部分,而具有非易失性的flash和抗熔FPGA則只有兩個主要的功耗組成部分(靜態和動態功耗)。

浪涌功耗——當基于SRAM的FPGA通電時,就會引起電流尖峰,這是因為易失性SRAM晶體管最初的邏輯狀態不確定。這種電流就是浪涌電流,并且為數百毫安級。基于Flash的FPGA由于采用了“上電即寫入(LAPU)”的配置方式,因此浪涌功耗非常小。

配置功耗——配置功耗發生在SRAM FPGA寫入程序的時候,這個時候系統加電啟動并從flash或者EEPROM存儲器中下載比特流數據。通常配置時間為幾百毫秒,并且電流強度為數百毫安。

后編程靜態功耗——該功耗是由于FPGA上大量的晶體管在器件沒有進行任何工作時也會出現少量的漏電流。這種漏電流在采用深亞微米技術制造的器件中占到了功耗量的很大一部分。而基于Flash的FPGA不需要任何“保持電流”來維持配置數據,因此與其他任何類型的FPGA相比,其靜態功耗都是最低的。

動態功耗——該功耗是器件正在工作的時候邏輯單元的開關電流引起的。動態功耗與工作電壓和開關頻率成正比。

FPGA節能技巧

選擇基于Flash的FPGA,因為它是真正的單芯片解決方案,無需配置支持,不存在浪涌功耗,而且靜態功耗低。

選擇具有低功耗模式的FPGA,也稱為睡眠模式,在該模式下時鐘服務電路處于關閉狀態,而且I/O被禁用,同時器件狀態保持不變。這就極大地降低了靜態功耗。

系統時鐘頻率對于FPGA器件的總體功耗有巨大的影響。時鐘頻率與帶寬性能有直接的關系,但是為了在功耗和吞吐量之間實現最佳的平衡,可以為不需要快速時鐘的元件提供一個較慢的始終頻率。對于那些與帶寬密切相關的元件,則提供更快的時鐘頻率。

圖:易失性存儲器FPGA與非易失性存儲器FPGA功耗曲線圖

評論