FPGA并行數字序列傳輸與接口技術的研究和應用

1 引言

本文引用地址:http://www.104case.com/article/150112.htmFPGA 技術在國內外經過歷時十余載的以硬件、系統及應用設計為主要內容的迅速發展 之后,其現代信息處理與控制技術的發展已開始崛起。顯然,一系列以乘法和加法為主的現 代信息處理算法能夠發揮FPGA 全并行算法的優勢,然而,算法中反復遇到的數字信息在節 點與模塊之間的序貫傳遞和交接,則給多路并行處理過程帶來了時差和異步的問題。例如, 系統辨識[1]的最小二乘參數估計算法中,信息壓縮矩陣與模型參數估計向量在并行地進行著 遞推計算,而無數次循環的中間結果則需要進行首尾交接;人工神經網絡[2]的訓練與執行中 同一層的所有節點的各路輸入在進行著并行的加權求和與活化函數的代入計算,但層與層之 間則需要進行節點間的數據交錯傳遞;同樣,Kalman 濾波[3]算法中的觀測向量、狀態向量、 控制向量與噪聲向量都在相鄰的兩個時刻之間進行著數據傳遞。由于在同一層次上被并行地 執行的各路的行進速度并不相同,交接的過程就需要互相等待,整個過程就需要統一控制, 否則將會出現數據丟失或傳輸阻塞。

本文將從硬件結構與功能的Verilog 語言數據流描述的角度,逐層討論問題的解決辦法 。

2.1 模塊內的數據傳輸

在一個模塊內,變量之間的數據傳輸接口的性質可分別用 reg(寄存功能,有延時性) 和wire(連線功能,無延時性)來定義。Reg 型常表示“always”( 觸發器)模塊的指定信 號,前者由后者通過使用行為描述語句來表達邏輯關系。

而wire 型常表示“assign”關鍵字的制定組合邏輯信號。當輸入輸出信號類型默認時自 動定義為wire 型。wire 型信號可以用作任何方程式的輸入,并且wire 型變量通常是用來表 示單個門驅動或連續賦值語句驅動的網絡型數據。

2.2 模塊間的數據傳輸

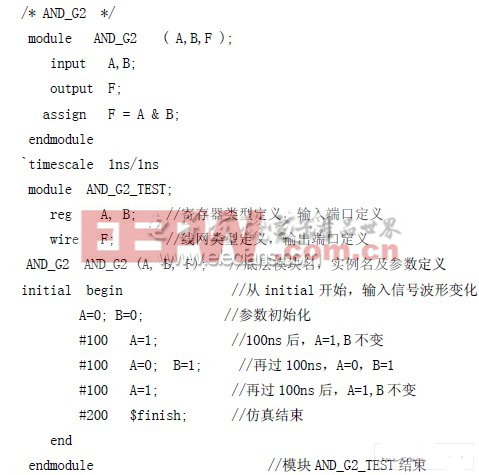

模塊間的數據傳輸接口例如延時輸出寄存器,它是一個使用了可控延時寄存器功能的AND 邏輯模塊(記作AND_G2)的數據流描述如下:

該程序中AND_G2_teST 為頂層模塊,AND_G2 作為一個單獨的模塊被頂層模塊所調 用。通過綜合控制,A、B 的輸入信號達到同步。

3 FPGA-信息處理實例—簡單人工神經網絡設計

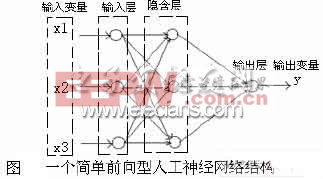

一個包括三個輸入、單個輸出、一個三節點隱含層的前向型人工神經網絡結構如圖1 所示。下面從多個角度討論數據的處理與傳輸。

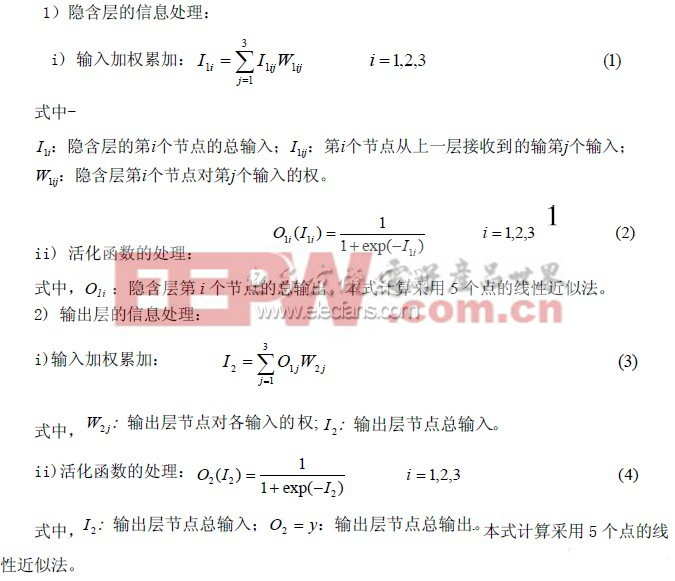

3.1 信息處理數學過程為:

評論