RAM讀寫時序限制解決方案

在逆塊掃描順序中,一些后續的系數可能需要在一開始時就準備好,而一些在前面次序的系數則可能在后續的時間使用,所以只有一個塊的所有數據都存儲完成后,才能進行后續的反變換,故至少要對一個塊的變換系數進行存儲。為了提高處理速度,后續的反變換模塊中將采用并行流水線輸入,因此存儲模塊此時不能采用有時序限制的RAM,本文采用了寄存器組實現。同時為了消除塊數據的準備延時,還采用了乒乓結構,即在設計中用了兩個寄存器組,這樣就可在處理當前一個塊系數的同時,用另一個寄存器組來存儲下一個塊反量化后的數據。

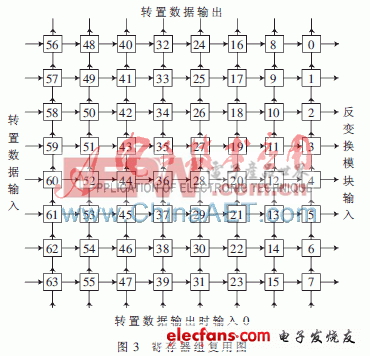

在反變換中也需要用到轉置存儲。為了節省資源,本設計采用了寄存器復用技術,即反變換中用到的轉置矩陣與逆掃描后用于存儲變換系數的矩陣復用,具體復用方法如圖3所示。

以上為一個寄存器組,包含64個13 bit的寄存器。最后一列為反變換模塊輸入,即當一個塊變換系數根據逆掃描順序存儲完后,連續8個時鐘周期讀取寄存器組最后一列,在每個時鐘周期向反變換模塊并行輸入8個13 bit的數據。第一列為轉置數據輸入端。考慮到反變換流水線及復用的問題,在連續2個時鐘周期讀取寄存器組最后一列輸入到反變換模塊后,轉置數據開始從第一列輸入,這樣可以滿足反變換內部的流水線問題,也可以達到寄存器復用的目的。第一行為轉置數據的輸出,最后一行在轉置數據輸出時賦值為零,這樣可以使轉置輸出和寄存器賦零同時進行,從而可以減少不必要的時鐘周期和資源。

2 仿真結果及分析

根據上述思想,采用Verilog HDL語言對算法進行了RTL級電路描述,并采用Altera公司的軟件Quartus II 8.0 對此算法進行了實現和仿真驗證,并將仿真結果與rm52j軟件的輸出結果進行了比較。Quartus II仿真結果如圖4所示,波形圖給出了一個塊的反量化和反變換輸出結果。rm52j的輸出結果如圖5所示,比較可見輸出結果相同。

本設計采用的是自頂向下和自下而上的混合設計方法,逆掃描、反量化和反變換過程是AVS系統中的一個模塊,局部的測試很難判斷出該模塊是否可以應用到整個解碼系統中去,所以此模塊亦在自己搭建的基于SoPC的AVS驗證平臺上進行了驗證。加入此模塊前,軟件處理一幀碼流時間與用此硬件模塊代替軟件模塊后的解碼時間如圖6所示,通過計算可知解碼速度提高約15%。

評論