便攜式高速數(shù)據(jù)采集系統(tǒng)設計

針對基于EPP協(xié)議的并行端口設備開發(fā)的特點與趨勢,開發(fā)了由A/D轉換器AD1671和FIFO存儲器ID7202構成的1.25MHz、12Bit的高速數(shù)據(jù)采集系統(tǒng),并通過IDT7202與EPP的接口電路實現(xiàn)了采集數(shù)據(jù)的高速回傳。介紹了EPP協(xié)議和該采集系統(tǒng)工作原理。

本文引用地址:http://www.104case.com/article/150020.htm關鍵詞: 增強并行口(EPP) 先進先出存儲器(FIFO) A/D轉換器AD1671

利用傳統(tǒng)的標準并行口(SPP)或RS232進行數(shù)據(jù)傳輸,其速度和靈活性受到很大限制。而增強型并行端口EPP(Enhanced Parallel Port)不但與SPP兼容,而且其最高傳輸速率可達ISA總線的能力(2MHz)。由于便攜式計算機日益普及,基于EPP協(xié)議開發(fā)的便攜式微機采集系統(tǒng)將會是一個發(fā)展趨勢。

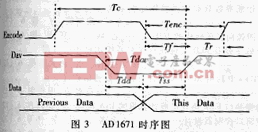

通常,低速的數(shù)據(jù)采集系統(tǒng)可不需要板上的數(shù)據(jù)緩存區(qū)。但當采集速率較高時,數(shù)據(jù)的回傳將占用CPU大量的時間,因而不可能進行其他的控制操作與數(shù)值處理,這時就需要足夠的緩存區(qū)來存放數(shù)據(jù)。我們在設計高速數(shù)據(jù)采集系統(tǒng)時采用了FIFO(First In First Out) IDT7202其管腳功能如圖1所示。它不但提供了存儲空間作為數(shù)據(jù)的緩沖,而且還在EPP并行總線和A/D轉換器之間充當一彈性的存儲器,因而無需考慮相互間的同步與協(xié)調。FIFO的優(yōu)點在于讀寫時序要求簡單,內(nèi)部帶有讀寫的環(huán)形指針,在對芯片操作時不需額外的地址信息。隨著FIFO芯片存儲量的不斷增加和價格的不斷下降,它將成為傳統(tǒng)數(shù)據(jù)存儲器件RAM、SRAM等的有力替代者。方案中的A/D轉換器采用了Analog Device 公司的AD1671,最大采集速率可達1.25MHz、12Bit無漏碼轉換輸出。

1 EPP協(xié)議簡介

EPP協(xié)議與標準并行口協(xié)議兼容且能完成數(shù)據(jù)的雙向傳輸,它提供了四種數(shù)據(jù)傳送周期:數(shù)據(jù)寫周期;數(shù)據(jù)讀周期;地址寫周期;地址讀周期。

在設計中我們把數(shù)據(jù)周期用于便攜機與采集板之間的數(shù)據(jù)傳輸,地址周期用于地址的傳送與選通。表1列出了DB25插座在EPP協(xié)議中的各腳定義。

表1 EPP信號定義

| EPP信號 | 方向 | DB25對應腳 | 描述 |

| nWrite | out | 1 | 低電平寫,高電平讀 |

| nDataSTB | out | 14 | 低有效,數(shù)據(jù)讀寫 |

| nAddrSTB | out | 17 | 低有效,地址讀寫 |

| AD[8:1] | Bi | 2~9 | 雙向數(shù)據(jù)/地址線 |

| GND | 18~25 | 地線 | |

| nReset | out | 16 | 低有效,外設復位 |

| NINTR | in | 10 | 外設中斷,對主機產(chǎn)生 |

| 一個中斷請求 | |||

| nWait | in | 11 | 握手信號,低表示可以開始一個 |

| 讀寫周期,高表示可以 | |||

| 結束一個讀寫周期 | |||

| Userdfn | in | 12/13/15 | 根據(jù)不同外設靈活定義 |

圖2是一個數(shù)據(jù)寫周期的例子。

(1) 程序執(zhí)行一個I/O寫周期,寫數(shù)據(jù)到Port4(EPP數(shù)據(jù)寄存器)。

(2)nWrite變低,數(shù)據(jù)送到串行口上。

(3)由于nWait為低,表示可以開始一個數(shù)據(jù)寫周期,nDataSTB變低。

(4)等待外設的握手信號(等待nWait變高)。

(5)nDataSTB變高,EPP周期結束。

(6)ISA的I/O周期結束。

(7)nWait變低,表示可以開始下一個數(shù)據(jù)寫周期。

可以看到,整個數(shù)據(jù)傳送過程發(fā)生在一個ISA I/O周期內(nèi),所以用EPP協(xié)議傳送數(shù)據(jù),系統(tǒng)可以獲得接近ISA總線的傳輸率(500k~2M byte/s)。

評論