FPGA在導(dǎo)彈上信息處理機中的應(yīng)用

引言

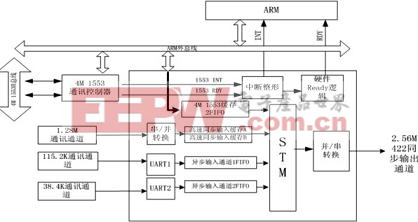

本文引用地址:http://www.104case.com/article/149976.htm信息處理機(圖1)用于完成導(dǎo)彈上多路遙測信息的采集、處理、組包發(fā)送。主要功能包括高速1553B總線的數(shù)據(jù)收發(fā) 、422接口設(shè)備的數(shù)據(jù)加載與檢測、多路數(shù)據(jù)融合和數(shù)據(jù)接收、處理、組包發(fā)送的功能。其中,總線數(shù)據(jù)和其他422接口送來的數(shù)據(jù)同時進(jìn)行并行處理;各路輸入信息按預(yù)定格式進(jìn)行融合與輸出;數(shù)據(jù)輸出速率以高速同步422口的幀同步脈沖為源,如果高速同步422口異常不影響總線數(shù)據(jù)和其它422口的數(shù)據(jù)融合與輸出功能。在CPU發(fā)生異常或總線數(shù)據(jù)異常時不影響其它422口數(shù)據(jù)的融合與輸出功能;能夠?qū)目偩€上接收的數(shù)據(jù)進(jìn)行二次篩選、組包,并發(fā)送往總線,供其它設(shè)備接收。

系統(tǒng)設(shè)計

CPU選擇

4M 1553B總線數(shù)據(jù)的采集,由4M總線智能通訊接口管理,經(jīng)CPU接收、組包,再回到4M總線,發(fā)送至FPGA進(jìn)行采集。CPU選擇Atmel公司的AT91FR40162S, 內(nèi)部自帶256KB的SRAM和容量為2M x 8b FLASH存儲器,主頻最高可達(dá)75MHz。該ARM的等待電路由硬件等待邏輯產(chǎn)生,在FPGA內(nèi)部實現(xiàn)。ARM外部中斷源主要有:4M 1553B通訊控制器中斷;20ms緩沖區(qū)切換中斷。其中,4M 1553B通訊控制器中斷信號經(jīng)過FPGA整形后送入ARM。20ms緩沖區(qū)切換中斷提供給FPGA內(nèi)部各個同步、異步通訊IP組幀狀態(tài)機用于緩沖區(qū)切換。

3路輸入數(shù)字量接口

3路輸入數(shù)字量,碼速率分別為:1.28Mbps、115.2Kbps、38.4Kbps的數(shù)據(jù)流,數(shù)據(jù)流在FPGA內(nèi)部經(jīng)過串并轉(zhuǎn)換將接收的數(shù)據(jù)存儲在數(shù)據(jù)緩沖區(qū)A和數(shù)據(jù)緩沖區(qū)B中,再經(jīng)過狀態(tài)控制機來控制數(shù)據(jù)的不斷更新。

同步422接口輸出

采用兩路單向RS422同步串行通訊接口,差分傳輸,一路為串行數(shù)據(jù),一路為時鐘數(shù)據(jù) ,采用雙線制傳輸。輸出碼速率2.56Mbps,15位加擾。

FPGA設(shè)計

當(dāng)3 路輸入數(shù)字量的數(shù)據(jù)流和4M的1553數(shù)據(jù)在20ms的時間內(nèi)傳輸時,所需的內(nèi)存約為10KB。

緩沖區(qū)存儲切換有2種方式:

1)當(dāng)1.28M的同步串行接口接收的數(shù)據(jù)個數(shù)達(dá)到64x100時切換;

2)由內(nèi)部的20ms定時器切換。

因此當(dāng)ARM異常后,能夠確保除4M總線數(shù)據(jù)之外的其它通道正常輸出。當(dāng)1.28M的同步串行接口異常后,F(xiàn)PGA內(nèi)的狀態(tài)機自動切換到內(nèi)部的20ms定時器進(jìn)行切換。FPGA設(shè)計及IP核通過SPARTAN3AN集成開發(fā)環(huán)境進(jìn)行仿真驗證。

FPGA選用Xilinx公司的SPARTAN3AN系列的XC3S700AN-4FG484,電壓1.2~3.3V,電流50mA~2A,主頻最高達(dá)70MHz以上。

地面單元測試儀的設(shè)計

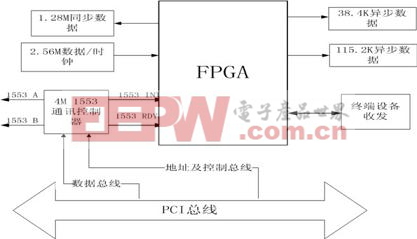

單元測試儀(圖2)主要完成對信息處理機各種功能和參數(shù)的測試,模擬產(chǎn)生彈上機的所有輸入信號,并測試其所有輸出信號,可用于信息處理機的生產(chǎn)調(diào)試、出廠測試和外廠維修。

圖2 地面單元測試儀框圖

單元測試儀由便攜式工控機內(nèi)插相應(yīng)PCI板卡和相應(yīng)軟件程序組成,PCI板卡為1塊COM通訊測試板卡,其主要實現(xiàn)和彈上高速內(nèi)總線4Mbps(或以上)1553B總線接口,在軟件的控制下,向彈上發(fā)送各種測試命令、并接收彈上機的測試結(jié)果。

系統(tǒng)實現(xiàn)

信息處理機的系統(tǒng)工作流程見圖3,具體包括:

(1)上電復(fù)位及初始化

上電后,F(xiàn)PGA和ARM同時復(fù)位,進(jìn)行初始化過程,其中FPGA初始化中, FPGA內(nèi)部寄存器和邏輯狀態(tài)的初始值、內(nèi)部緩沖區(qū)數(shù)據(jù)清零依靠復(fù)位信號來完成,其中的“FPGA參數(shù)設(shè)定”由監(jiān)控程序負(fù)責(zé)執(zhí)行或由FPGA使用缺省參數(shù)完成。

如果上電或復(fù)位時出現(xiàn)問題,F(xiàn)PGA使用缺省參數(shù)自動初始化所有參數(shù)并自動進(jìn)行后續(xù)工作。

(2)20ms緩沖區(qū)切換信號同步

完成初始化后,F(xiàn)PGA內(nèi)部的“20ms緩沖區(qū)切換信號”生成邏輯,自動執(zhí)行和“1.28M同步輸入串口”的同步過程,同步過程中不向外發(fā)送任何數(shù)據(jù),一旦同步后,會給出同步鎖定信號Sync Locked=“1”,所有通道的數(shù)據(jù)采集工作均開始,進(jìn)入遙測信息接收過程。

(3)遙測信息接收

通道的數(shù)據(jù)采集都以FPGA內(nèi)部產(chǎn)生的“20ms緩沖區(qū)切換信號SwitchBuf”為20ms周期標(biāo)志進(jìn)行緩沖區(qū)的切換(雙端口),分別為A,B兩個緩沖區(qū)。

1.28M通道在20ms內(nèi)應(yīng)完成32x100=3200 Bytes的數(shù)據(jù)接收。并根據(jù)字計數(shù)器反轉(zhuǎn)當(dāng)前的SwitchBuf信號。

4M 1553B通道應(yīng)由ARM完成4M 1553B總線遙測數(shù)據(jù)的接收、過濾、打包,形成20ms內(nèi)約1500 Bytes的遙測數(shù)據(jù)包填入分配給它的包緩沖區(qū),由FPGA自動生成對應(yīng)的包長度信息放入一個包長度FIFO中。此后,ARM重新開始下一20ms數(shù)據(jù)接收工作,,如此反復(fù)循環(huán)下去。組幀狀態(tài)機(MFSTM)在組幀過程中,一旦發(fā)現(xiàn)包長度FIFO不空,就從包緩沖區(qū)FIFO中讀取對應(yīng)長度的數(shù)據(jù)包,按照規(guī)定格式和位置填入數(shù)據(jù)融合表。

圖3 信息處理機工作流程

38.4K異步串行輸入通道由FPGA的UART IP核完成串行輸入數(shù)據(jù)的接收,IP核根據(jù)字間隔是否超過2個字的接收時間來判斷是否完成一幀的接收,原理和1553總線數(shù)據(jù)的接收相同。

115.2K異步串行輸入通道由FPGA的UART IP核完成串行輸入數(shù)據(jù)的接收.緩沖區(qū)由一個FIFO組成。組幀狀態(tài)機會隨時查詢該FIFO空滿狀態(tài),若不空,則就開始連續(xù)的讀取過程,每間隔200μs從FIFO中讀取一個數(shù)據(jù)并按照規(guī)定格式和位置填入數(shù)據(jù)融合表,直到該FIFO的數(shù)據(jù)取完為止,若為空,則新幀對應(yīng)通道的位置數(shù)據(jù)填零。

(4)組幀

組幀工作即遙測數(shù)據(jù)的數(shù)據(jù)融合,將各路遙測信息按照給定的數(shù)據(jù)融合格式組織成一個完整的100幀(1幀200us,100幀20ms)格式進(jìn)行發(fā)送,該功能由設(shè)計在FPGA內(nèi)部“組幀狀態(tài)機(MFSTM)IP”完成。

(5)數(shù)據(jù)融合表

上電復(fù)位后,組幀狀態(tài)機MFSTM等待同步鎖定信號Sync Locked=“1”后開始工作,并根據(jù)20ms緩沖區(qū)切換信號SwitchBuf進(jìn)行周期性的切換。按照數(shù)據(jù)融合表設(shè)計好的順序依次訪問1.28M同步輸入串口緩沖區(qū)、4M 1553B總線數(shù)據(jù)緩沖區(qū)、115.2K異步輸入串口緩沖區(qū)、38.4K異步輸入串口緩沖區(qū)等等,并讀取指定數(shù)量的數(shù)據(jù)依次填入本次20ms的數(shù)據(jù)融合表中,重復(fù)100次,從而完成表中1~100行數(shù)據(jù)的填寫。數(shù)據(jù)融合表的數(shù)據(jù)結(jié)構(gòu)設(shè)計成FIFO, 使用FIFO可以平衡快速的組幀狀態(tài)機和慢速的發(fā)送狀態(tài)機之間的速度差異,使發(fā)送的數(shù)據(jù)流保持在2.56Mbps的波特率之下,持續(xù)發(fā)送。

(6)發(fā)送

數(shù)據(jù)融合表的發(fā)送則由“發(fā)送狀態(tài)機(SendSTM) IP”完成。它以數(shù)據(jù)融合表FIFO、2.56M發(fā)送時鐘為輸入,一旦啟動就不再停止。發(fā)送狀態(tài)機首先查詢數(shù)據(jù)融合表FIFO, 若FIFO為空,則等待;若FIFO不空,則以2.56M/8的固定時鐘頻率持續(xù)讀取數(shù)據(jù)融合表FIFO的數(shù)據(jù),再送入“15段加擾器”進(jìn)行加擾,加擾后的數(shù)據(jù)和時鐘經(jīng)RS-422驅(qū)動電路轉(zhuǎn)化為RS-422差分形式發(fā)送給加密器,即2.56M輸出。

(7)1.28M同步輸入串口故障檢測

FPGA中的故障檢測單元(FDU)負(fù)責(zé)檢測1.28M同步輸入串口的輸入信號是否正常。當(dāng)故障檢測單元FDU發(fā)現(xiàn)1.28M同步輸入串口產(chǎn)生的SwitchBuf信號的周期和晶振產(chǎn)生的20ms時鐘周期誤差超過△T(如±2ms),則認(rèn)為1.28M同步輸入串口故障,立即將SwitchBuf信號切換到由晶振分頻產(chǎn)生的20ms時鐘上。

系統(tǒng)仿真

以下為相關(guān)軟件對系統(tǒng)主要功能進(jìn)行的仿真:

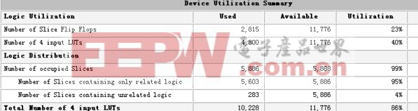

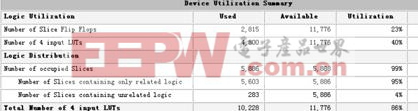

圖4 ISE編譯后得出的FPGA資源利用情況

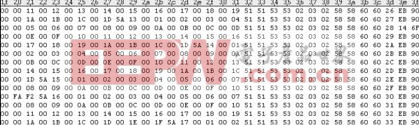

圖5 數(shù)據(jù)融合表的仿真結(jié)果

數(shù)據(jù)融合表的結(jié)構(gòu)為100行,64列,第1-32列為高速同步接口數(shù)據(jù),第33-50列為總線數(shù)據(jù),第51、52列分別為115.2K、38.4K接口數(shù)據(jù),還有少量模擬量數(shù)據(jù)、全幀計數(shù)、同步碼組等。

圖6 數(shù)據(jù)融合表輸入及輸出的對比

由于組幀速度遠(yuǎn)比讀出速度快,所以分兩個圖顯示。

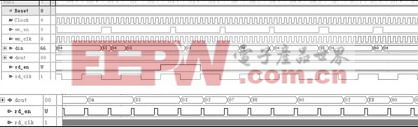

圖7 2.56M發(fā)送數(shù)據(jù)

結(jié)語

用FPGA代替常規(guī)處理器實現(xiàn)多路數(shù)據(jù)的采集、融合并實時發(fā)送,利用FPGA豐富的可編程邏輯資源和內(nèi)部存儲器進(jìn)行邏輯設(shè)計,大大減少了外圍元器件種類和數(shù)量,提高了系統(tǒng)的處理和I/O帶寬。

同時,F(xiàn)PGA在航天領(lǐng)域的應(yīng)用也推動了可編程技術(shù)的發(fā)展。

評論