嵌入式系統應用中NV SRAM存儲器的應用

如果需要尋址更多的數據存儲器,只需在微處理器的數字接口簡單地添加高位地址線即可,圖中所示的8051支持64kB(A0-A15)的尋址空間,最高5位地址線(A16-20)和片選引腳可用于選擇64kB存儲器頁,對于編程器而言采取讀、寫子程序能使大容量存儲變得完全透明。上述操作不適用于程序存儲器,由于微處理器取代碼時不允許頁選擇,它按照16位地址取指令,可能選擇錯誤的頁碼。如果圖1選用DS1245,則只能尋址到一半的數據。如果用A16建立第二頁存儲器,當存取第二頁的數據時會導致微控制器取第二頁的指令。

具體設計中需注意以下事項

1。檢查總線時序

控制信號是否提供了足夠的讀、寫時間,要特別注意系統的時鐘速率,因為控制信號的時序總是取決于時鐘速率。如果總線控制信號速度過高,大多數微處理器能夠展寬時鐘,降低數據存儲速率。

2。確認總線控制信號在上電或掉電時的狀態

如果Vcc高于門限電壓時CE=WE=0,當前地址的數據在沒有正常寫操作的情況下將被破壞。如果系統僅對本地可尋址空間尋址,要確保總線控制信號在復位狀態處于禁止狀態、保證數據不被破壞。當采用擴展尋址時,需保證I/O信號控制CE和WE在上電或掉電狀態下均處于高電平。利用CPU監控電路能夠保證微處理器在NVSRAM處于電池備份模式時不會訪問NVSRAM。這時模塊內的片選信號為高電平,與外部CE信號無關,模塊內的SRAM將拒絕任何外部訪問。

微處理器利用NVSRAM存儲程序

利用NVSRAM存儲程序時有兩點值得特別考慮:1。NVSRAM必須具有足夠快的存取速率、不需要降低時鐘速度。2。Vcc低于電壓監視門限時,不能訪問NV

SRAM。微處理器必須在每個機器周期取指令(通常每個機器周期占用一個以上的時鐘周期),如果程序存儲器速度較慢、需降低時鐘速率以符合存儲器存取速率的要求。顯然,這種情況制約了系統性能。目前,5V高速NVSRAM的存取時間可以達到70ns,3。3V的NVSRAM可以達到100ns,能夠符合大多數應用的要求。

利用復位門限接近Vcc的CPU監控電路能夠避免微處理器在NVSRAM就緒之前對其進行讀、寫操作,此外,Vcc噪聲有可能導致電壓瞬間跌落至Vcc門限以下,造成器件在瞬間干擾時無法讀取。鑒于這一點,建議在靠近模塊的Vcc引腳安裝去耦電容。由于市場上可以很容易找到5%電壓容差的CPU監控芯片,因此,采用電壓容差為10%的NVSRAM可簡化設計,現有的3。3V和5V的器件均可滿足這種要求。

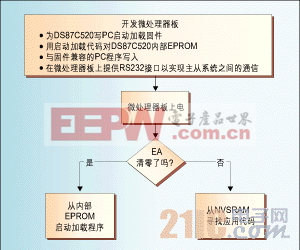

如上所述,NVSRAM不適合作便攜數據的載體,當器件脫離具有實際意義的電路時容易丟失數據。最好是在線進行器件編程,為解決嵌入式系統的在線編程問題,可以簡單構建一個導入裝載器,流程如圖3所示。

導入器在切換存儲器(從微控制器的內部EPROM切換到外部NVSRAM)時工作,存儲器內部電路通過RS232端口接收數據,將數據復制到適當地址的NVSRAM內。實現該流程的簡單數據格式是Intel的十六進制文件格式,因為這種對數據和數據地址的編碼格式是許多匯編語言采用的標準文件格式。EA引腳置“1”,選擇內部存儲器,此時PC機可以通過一個RS232串口給微控制器發送數據。微控制器將代碼寫入NVSRAM后即可關閉電源、清EA引腳,當再次上電時微處理器便開始執行存放在NVSRAM內的代碼。一旦完成了最初的硬件和軟件開發,就可以方便地進行快速編程,大大縮短產品開發周期。這種方案的缺陷是對于不同產品的開發必須保持固定的晶振頻率,以保證串行端口的波特率能夠由PC機軟件調節。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論