基于DSP開發系統設計與實現

摘要:為了設計一個性能穩定的DSP開發系統,利用TI公司最新推出的TMS320F28335作為微處理器,該芯片為32位浮點型DSP。在采用浮點DSP設計系統時,不需要考慮處理的動態范圍和精度,比定點DSP在軟件編寫方面更容易,更適合采用高級語言編程。外圍電路主要包含電源電路、RAM擴展電路、晶振電路和復位電路,用來輔助DSP的工作。利用電源管理芯片設計電源電路,可以有效解決其他型號的DSP對上電順序的要求;擴展的外部RAM可以使程序的調試與下載更加方便。利用外部時鐘源作為時鐘輸入,使其輸入時鐘更加穩定的同時,也可為具有相同時鐘的多個DSP使用。利用三端監控芯片來實現系統的手動復位和自動復位,使系統的穩定性大大提高。

關鍵詞:TMS320F28335;浮點型;動態范圍;數字信號處理器

TMS320F28335是TI公司最新推出的32位浮點型DSP,可直接參與浮點型數據的運算,無需Q格式的轉換,其主要特點為:高性能的靜態CMOS技術,在最高為150 MHz振蕩頻率下,指令周期為6.67 ns;高性能的32位CPU,單精度浮點運算單元(FPU),采用哈佛總線結構,能快速中斷響應和處理,并有統一的存儲器規劃,可用C/C++語言實現復雜的算法;控制時鐘系統具有片內振蕩器和看門狗定時器模塊,支持動態改變鎖相環(PLL)的參數值以改變CPU的輸入時鐘頻率;8個外部中斷,相對于TMS320F281x系列DSP,無專門的中斷引腳;支持58個外設中斷的外設中斷擴展寄存器(PIE),管理片上外設和外部引腳引起的中斷請求;增強型的外設模塊;12位A/D轉換器,可實現16通道的數據轉換;88個可編程的分時復用GPIO引腳;低功耗模式,1.9 V或1.8 V內核,3.3 V I/O供電。設計一個集這些優點于一身的DSP開發系統,對于初學者和開發人員有著重要的意義。本文首先分析和對比DSP電源設計方案,選擇合適的設計方案并詳細介紹;然后設計存儲器擴展電路,并給出其存儲范圍;通過對比時鐘電路的各種實現方案,擇優選擇適合于該系統的時鐘電路并詳細介紹;最后給出復位電路的設計方法和提高硬件抗干擾能力的措施。

1 系統電源設計

TI公司的DSP系列一般都有獨立的內核和I/O電源。因為在DSP在系統中要承擔大量的數據計算,在CPU內部,部件的高頻率的轉換會使系統功耗大大增加。所以采用雙電源的供電方式,F28335一路為I/O提供3.3 V電壓,另一路為CPU內核提供1.8 V或1.9 V電壓,這樣可大大降低系統的功耗。

電源設計方案一:兩路電源獨立沒計,其優點是調試方便且互不干擾,缺點是不能適合某些對上電次序有要求的DSP,成本較高。

電源設計方案二:采用TI公司的雙路低壓差電壓調整器。TPS767D3xx系列電壓調整器是TI公司為DSP開發的電源管理芯片,通過簡單的設計,可以適合某些系列DSP內核與I/O電壓的上電順序問題。

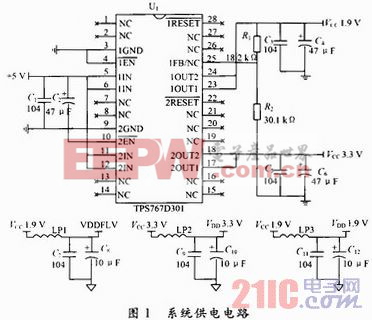

本設計采用方案二,利用TI公司的雙路低壓差電壓調整器TPS767D301。它的特點是:帶有可獨立供電的雙路輸出,一路固定輸出為3.3 V,另一路可以在1.5~5.5 V調整,每路輸出電流范圍為0~1 A;電壓差大小與輸出電流成正比,且在最大輸出電流為1 A時,最大電壓差僅為350 mA;超低的靜態電流85μA,器件無狀態時,靜態電流僅為1μA。

TMS320F28335對內核和I/O的上電順序沒有要求,可以同時上電,使得電源電路大大簡化。具體電路如圖1所示。

評論