采用Max+PlusⅡ平臺的CMI編碼器的設計方案

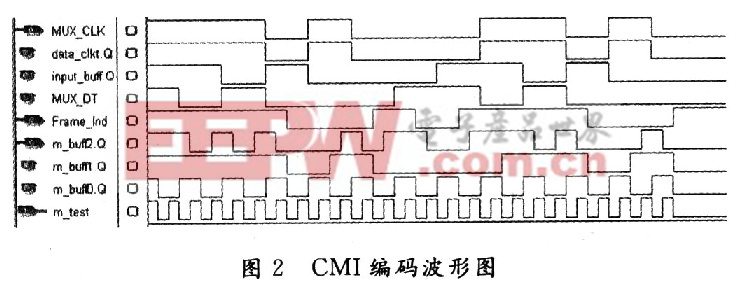

其中:m_test:產生的m序列;

本文引用地址:http://www.104case.com/article/149097.htmMUX_DT:CMI編碼輸出;

MUX_CLK:原始時鐘。

3 仿真結果

在Max+PlusⅡ平臺下對CMI編碼進行編譯和仿真,最后得到CMI編碼仿真結果。圖2是CMI碼編碼波形圖。

在時鐘MUX_CLK驅動下工作,m_test是產生的m序列1011100,MUX_的DT為CMI編碼輸出,可以看到,編碼為11010011000101,有一定延時,但編碼完全正確。

4 結語

該設計詳細介紹了基于CPLD的CMI編碼的實現方法。提出利用原始信號的二分頻后的信號求非賦值給編碼輸出,得到“0”的編碼,利用緩存對“1”的個數進行記錄,而對“1”進行編碼的編程思路,利用VHDL進行程序設計實現,在Max+PlusⅡ平臺下對設計結果進行仿真,結果完全正確。

實踐表明,運用CPLD實現CMI編碼具有軟件開發周期短、成本低、執行速度高、實時性強、升級方便等特點,而且可以把該電路和其他功能電路集成在同一塊CPLD/FPGA中,減少了外接元件的數目,提高了集成度,而且有很大的編程靈活性,很強的移植性,因此有很好的應用前景。

評論