基于DSP+FPGA的磁鐵電源控制器的設(shè)計(jì)

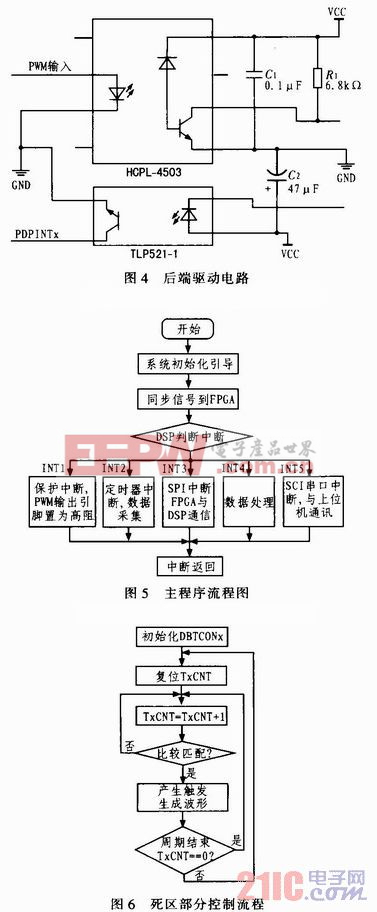

2.4 驅(qū)動(dòng)電路的設(shè)計(jì)

圖4的驅(qū)動(dòng)電路中高速光耦HCPL-4503快速實(shí)現(xiàn)信號(hào)的轉(zhuǎn)換和隔離,而故障信號(hào)經(jīng)低速光耦TLP521-1隔離后送至PDPINTx引腳,PWM輸出引腳變?yōu)楦咦钁B(tài),同時(shí)產(chǎn)生一個(gè)中斷,封鎖驅(qū)動(dòng)信號(hào),關(guān)閉功率開(kāi)關(guān)管。本文引用地址:http://www.104case.com/article/148555.htm

3 控制器軟件設(shè)計(jì)

當(dāng)發(fā)生中斷時(shí),DSP的CPU會(huì)根據(jù)中斷響應(yīng)的優(yōu)先級(jí)和中斷向量表判斷,跳至相應(yīng)的子程序執(zhí)行,實(shí)現(xiàn)各自的功能。圖5為主程序的流程圖。

為防止上下兩橋臂開(kāi)關(guān)器件同時(shí)導(dǎo)通,驅(qū)動(dòng)波形需要具有一定的死區(qū)時(shí)間。設(shè)置DSP死區(qū)控制寄存器DBTCONx[8-11]位死區(qū)定時(shí)器周期為m,DBTCON位的死區(qū)定時(shí)器預(yù)定標(biāo)因子為x/p,若通用定時(shí)器時(shí)鐘周期為t,則死區(qū)時(shí)間ts=m*p*t。死區(qū)部分控制流程如圖6所示。

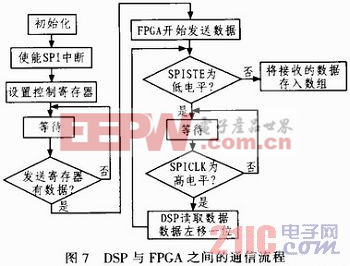

圖7為DSP和FPGA之間的通信流程。波特率的配置通過(guò)對(duì)DSP的SPIBRR寄存器的編程實(shí)現(xiàn),在SPI接口設(shè)計(jì)時(shí)應(yīng)注意使用系統(tǒng)時(shí)鐘對(duì)SCLK信號(hào)進(jìn)行同步以減少SCLK引起的通信錯(cuò)誤。

4 結(jié)束語(yǔ)

采用DSP+FPGA架構(gòu)的磁鐵電源控制器兼有兩種信號(hào)處理芯片的優(yōu)越性,有效的提高了運(yùn)算速度和精度。在后續(xù)的研究中根據(jù)需要設(shè)置相應(yīng)參數(shù),選擇合適的控制算法,以滿(mǎn)足磁鐵電源輸出極低紋波和受精確控制的電流。

評(píng)論