采用CPLD的片內(nèi)環(huán)形振蕩器的方案設(shè)計(jì)

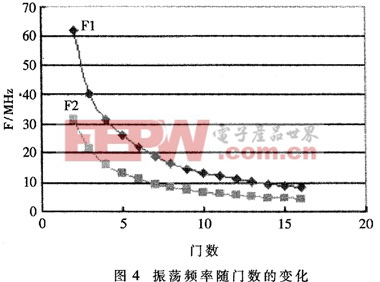

表1數(shù)據(jù)表明,通過增加門電路的數(shù)量可以有規(guī)律地減小振蕩電路的工作頻率,由每個(gè)邏輯單元實(shí)現(xiàn)的門電路單元延時(shí)tpd在7.5~10ns之間。

本文介紹的基于CPLD的片內(nèi)振蕩器設(shè)計(jì)方法,在改變?cè)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/振蕩器">振蕩器電路中門電路數(shù)量時(shí),可以有規(guī)律地將振蕩頻率控制在8MHz~62MHz范圍內(nèi)。振蕩器的片內(nèi)設(shè)計(jì)使基于CPLD的片上系統(tǒng)(SoC)設(shè)計(jì)無需外接時(shí)鐘信號(hào)源,加大了系統(tǒng)的集成度并降低了設(shè)計(jì)成本。本方法有很大的通用性,可以方便地在不同CPLD芯片間移植。仿真和測(cè)試數(shù)據(jù)表明該設(shè)計(jì)方法具有正確性和可行性。本文引用地址:http://www.104case.com/article/148424.htm

評(píng)論