基于FPGA的正交相干檢波方法及實現

2 基于FPGA的實現方案

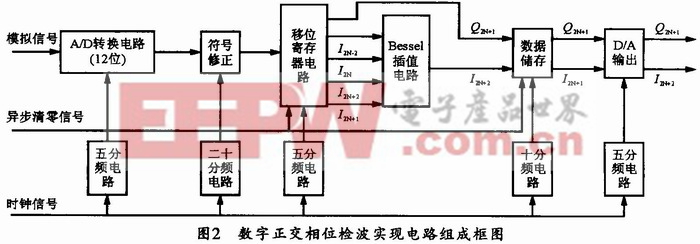

首先將輸入FPGA的一路12位數字信號中的每一位都與時鐘信號進行異或運算,以使I’(n)=x(2n)(-1)n和Q’(n)=x(2n+1)(-1)n+1,從而達到符號修正的目的。經過修正,輸出的數字信號序列是一個由I的偶數項和Q的奇數項交替出現所組成的序列,即:I0,Q1,I2,Q3,I4,Q5,…,I2n,Q2n+1…。為實現Bessel插值,還需要得到某時刻Q2n+1值所對應的I的偶數項(I2n-2,I2n,I2n+2和I2n+4)。鑒于移位寄存器有延時功能,可使用12片移位寄存器74164取出I的偶數項序列,同時分離的還有相應的Q2n+1一路信號。接著,I的偶數項序列經過加法器電路進行有符號加、減法運算。由于Bessel插值中的分母均為2的整數冪,因而用右移來實現2的整數冪除法非常方便。其實現框圖如圖2所示。本文引用地址:http://www.104case.com/article/148389.htm

該FPGA實現方法,由于只涉及移位、簡單門和加減法運算,因此,用FPGA實現起來很方便,也可以獲得較高的運算速率。

3 基于FPGA的硬件仿真結果

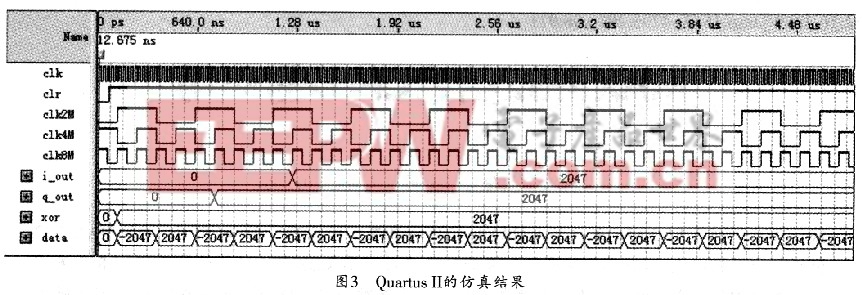

為便于觀察,仿真時可設定輸入信號A (t)為常數,A/D的采樣率fs為8 MHz來對信號進行中頻采樣并插值,以得到二路正交信號。運用QuartusⅡ的仿真結果如圖3所示。

圖3中,data為A/D采樣后的輸入信號,xor為符號修正后的信號,i_out,q_out為輸出信號。

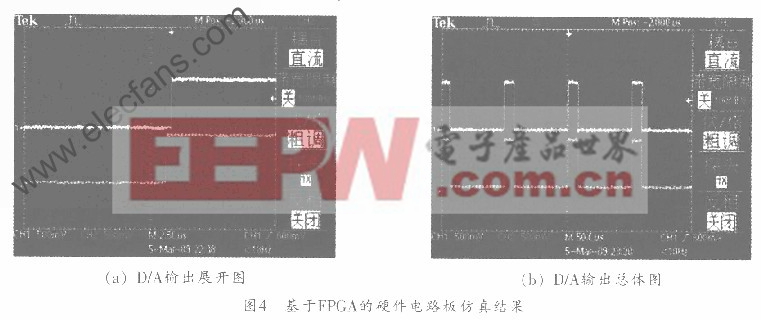

之后,將仿真程序下載到電路板中的FPGA(使用的是ALTERA公司的EPlC3T144C7芯片)中,便可用示波器觀察到如圖4所示的仿真結果。

從圖4可以看出,I,Q兩路輸出為相似的波形,符合前面的設定A(t)為常數;其中圖4(a)為圖4(b)的展開圖,由圖4可以看出,I,Q兩路

信號存在相位上的差異。

4 結束語

本文詳細介紹了中頻直接正交采樣及Bessel插值理論,并基于這一理論,用FPGA將一路中頻信號分解成了兩路正交數字信號,本文同時重點給出了用FPGA實現這一過程的詳細方案。

評論