基于FPGA的短幀Turbo譯碼器的實現

本文引用地址:http://www.104case.com/article/148285.htm

3.1 數據量化

在通信系統中,譯碼器的接收數據并不是連續不變的模擬量,而是經過量化后的數字量。接收數據的量化會引入量化噪聲,從而影響譯碼的性能。所以,接收數據量化的精度直接影響到譯碼的性能。由參考文獻[5~6]可知,采用3位量化精度就能得到與沒有經過量化的浮點數據相近的譯碼性能。為了簡化FPGA的設計,本文采用了統一的定點量化標準F(9,3),即最高位為符號位,整數部分8位,小數部分3位。由此,前后遞推項(9)、(10)式的初始值可表示為:

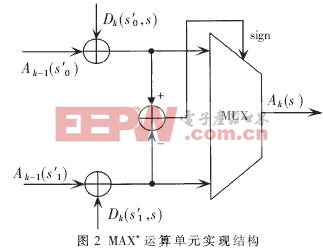

3.2 MAX*運算單元

由前面的MAX-LOG-MAP算法介紹可知,MAX*運算單元是整個譯碼的主要運算單元,它與viterbi譯碼的ACS(加比選)運算單元一樣,先分別進行加法操作,然后對所得結果進行比較,最后將較小的一個結果作為運算結果輸出。實現結構如圖2所示。

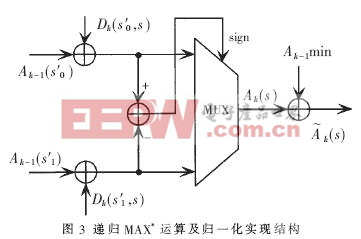

3.3 前后向遞推運算單元

由公式(5)~(8)可知,前后向遞推單元除了需要進行MAX*與運算外,還需要進行歸一化處理。為得到較快的運算速度,首先,計算上一時刻所有狀態的最小值,然后對當前時刻的每一狀態進行MAX*運算,并將運算結果減去上一時刻的最小狀態值,即得到當前時刻遞推各狀態的歸一化值。實現結構如圖3所示。

評論