DSP設計流程

引言

本文引用地址:http://www.104case.com/article/148249.htm世界正處于高科技下一波快速增長的開端,AccelChip公司 Dan Ganousis DSP 已經成為業界公認的、將按指數增長的技術焦點。

目前,大多數DSP設計已經能在半導體生產商(如T1、ADI、Freescale等)提供的通用DSP芯片上實現。通用處理器的價格相對比較便宜,并且有高質量和廉價的編程工具、方便快速實現DSP算法的支持,但開發人員更希望在原型創建和調試過程中能進行重新編程。

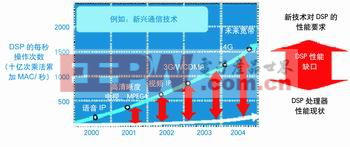

圖1 通用DSP處理器的性能與通信領域需要的DSP處理性能的比較

速度的需要

現在,對電子系統的性能要求已經超過了通用DSP處理器的能力。圖1顯示了由寬帶網絡市場驅動的對DSP算法的性能需求與通用DSP處理器性能的差異。可以看出通用DSP的性能容量與新的寬帶通信技術的需求之間的差距正以指數速率擴大。

傳統上DSP開發者可以獲得的改變通用DSP處理器性能的唯一方法就是將DSP算法注入到ASIC中,以達到加速硬件的目的。然而這種ASIC的解決方法實現起來非常困難,而且在ASIC上實現DSP算法是以犧牲可重編程的靈活性為代價的,同時還需要大量的非重復設計費用、漫長的原型初始化,以及購買大量昂貴的集成電路設計工具等。

隨著先進的FPGA架構如Xilinx Virtex-II和Altera Stratix-II的引入,DSP設計者可以獲得一種把通用DSP處理器的所有優點與ASIC的先進性能綜合在一起的新型硬件。這些新型的FPGA架構可以優化DSP的實現,并能提供滿足現今電子系統所必需的處理能力。

FPGA的優越性表現在它能允許DSP設計者做到“使結構適應算法”,設計者能夠根據實現系統性能的需要最大限度地使用FPGA內部的并行資源。而在通用DSP處理器中資源是固定的,因為每個處理器只包含一些數量有限的類似乘法器一樣的基本運算功能,設計者必須做到“使算法適應結構”,因而無法達到在FPGA中能夠獲得的性能。

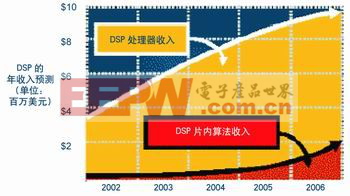

圖2 全球DSP收入預測

半導體工業的亮點

圖2顯示了整個DSP市場和片內算法市場(由FPGA、結構化ASIC和ASIC幾部分組成)的年收入預測。其中,DSP片內算法市場今后三年內將以高于42%的年增長率增長,是整個半導體領域增長最快的部分。

現在DSP的設計團隊所面臨的挑戰和二十世紀九十年代ASIC的設計者所面臨的類似-DSP開發組如何用目標FPGA的設計方法代替通用DSP;如何去開發所需要的新的設計技巧;如何完善公司的設計流程;怎樣才能提出新的DSP算法的實現方法,同時又不危及當前產品的開發計劃。或許更重要的是,管理者怎樣才能夠使災難性結果發生的可能性降低到最小。

AccelChip公司認為DSP的未來取決于新型設計方法的采用,而這種方法必須能使公司滿足DSP市場對上市時間、成本的苛刻要求。和ASIC、FPGA的產生一樣,對DSP變革的方式就是采用真正的、自上而下的設計流程。

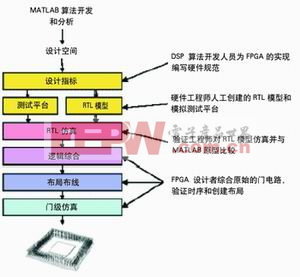

圖3 傳統的DSP設計流程

評論